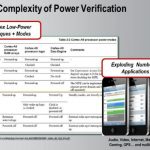

I can’t imagine that any SoC today is designed without taking intense interest in how much power the chip will consume, whether it is destined for a mobile phone or tethered in a cloud datacenter. One challenge with power is that adding features like voltage islands or power-down areas require changes to the netlist such as… Read More

Tag: low power

High and Low: High Level Synthesis and Low Power

It is so widely accepted that it is already a cliche to say that “power is the new timing.” With more and more chips, the major challenge is not so much to meet timing but to meet timing without blowing out the power budget. Otherwise, you could just crank up the clock rate.

I’m going to be lazy so you can insert your … Read More

HiFi Mini, Always Listening

Next week it is the Consumer Electronics Show (CES) in Las Vegas and so there are announcements around the areas where consumer overlaps with semiconductor, which these days is primarily mobile. Then in February in Barcelona is Mobile World Congress, which is even more focused on mobile. Expect more announcementst there.

Currently… Read More

Apache Power Artist Capabilities II

This is the second part of my discussion with Paul Traynar, Apache’s PowerArtist guru. The first part discussed sequential reduction capabilities. Part I was here.

There are two big challenges with doing power analysis at the RTL level. Firstly, how do you get an accurate enough model of what the design will dissipate given… Read More

Apache Power Artist Capabilities I

I sat down last week with Paul Traynar who was over from UK. He is Apache’s PowerArtist guru. The first thing we talked about was PowerArtist’s sequential power reduction capabilities.

Forward propagation of enables means that when a register is clock gated and feeds a downstream register then that register can be… Read More

Sequential Power Optimization

Calypto has an interesting webinar coming up about Minimizing RTL Power Through Sequential Analysis. It is next Tuesday December 4th at 11am.

Insert standard paragraph about how power is the new timing, everyone worries about power, battery life in smartphones, half-empty datacenters.

You probably already know about clock… Read More

Addressing the Nanometer Digital Design Challenges! (Webinars)

Optimizing logical, physical, electrical, and manufacturing effects, Cadence digital implementation technology eliminates iteration without sacrificing design quality by addressing timing sensitivity, yield variation, and leakage power from the start. … Read More

Apache Low Power Webinars

For those of you who didn’t get to DAC you can catch up on low power issues with Apache’s series of low-power webinars taking place late in July. All webinars are at 11am Pacific Time. Full details and registration on the Apache website here.… Read More

Apache Ansys Update 2012

Apache is one of the brightest stars in the EDA universe. Paul McLellan has done a nice job covering them before and after the Ansys acquisition. Check out the Apache SemiWiki landing page HERE. The Apache wikis are also very well done and it has been a pleasure working with the Apache marketing team. Expect more innovative things … Read More

LTE-Advanced Handsets for 4G

Due to a lot of somewhat aggressive marketing by carriers, you might think that 4G wireless is already here. After all, wasn’t 3G ages ago? But in fact true 4G handsets won’t really be available until 2015/6. But to make that schedule, first silicon needs to be available late this year or early next, to allow one or two … Read More