imec XTCO (Cross-Technology Co-Optimization) is the natural successor to DTCO and STCO in an era where no single layer of the stack can deliver scaling alone. Instead of optimizing devices, interconnect, packaging, architecture, and software in isolation, XTCO treats them as one tightly coupled system with a shared budget … Read More

Tag: imec

3D IC Design Ecosystem Panel at #61DAC

At #61DAC our very own Daniel Nenni from SemiWiki moderated an informative panel discussion on the topic of 3D IC Design Ecosystem. Panelists included: Deepak Kulkarni – AMD, Lalitha Immaneni – Intel Foundry, Trupti Deshpande – Qualcomm, Rob Aitken – CHIPS, Puneet Gupta – UCLA, Dragomir Milojevic – imec. Each panelist had a brief… Read More

SEMICON West- Jubilant huge crowds- HBM & AI everywhere – CHIPS Act & IMEC

– We just finished the most happy SEMICON West in a long time

– IMEC stole the show- HBM has more impact than size dictates

– Has Samsung lost its memory mojo? Is SK the new leader?

– AI brings new tech issues with it – TSMC is still industry King

Report from SEMICON West

The crowds at Semicon West were both… Read More

IEDM 2023 – Imec CFET

At IEDM 2023, Naoto Horiguchi presented on CFETs and Middle of Line integration. I had a chance to speak with Naoto about this work and this write up is based on his presentation at IEDM and our follow up discussion. I always enjoy talking to Naoto, he is one of the leaders in logic technology development, explains the technology in … Read More

CEO Interview: Harry Peterson of Siloxit

Harry Peterson is a mixed-signal chip designer with a BS in Physics from Caltech. He managed IC design groups within Fairchild, Kodak, Philips, Northern Telecom, Toshiba and Pixelworks. During sabbaticals he helped fly experiments on NASA’s orbiting satellite observatory (OSO-8) and build telescopes in the Canary… Read More

SPIE 2023 – imec Preparing for High-NA EUV

The SPIE Advanced Lithography Conference was held in February. I recently had the opportunity to interview Steven Scheer, vice president of advanced patterning process and materials at imec and review selected papers that imec presented.

I asked Steve what the overarching message was at SPIE this year, he said readiness for … Read More

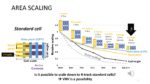

IEDM 2022 – Imec 4 Track Cell

At the IEDM conference in December 2022, Imec presented “Semi-damascene Integration of a 2-layer MOL VHV Scaling Booster to Enable 4-track Standard Cells,” I had a chance to not only read the paper and see it presented, but also to interview one of the authors Zsolt Tokie.

Logic designs are built up by standard cells such as inverters,… Read More

SEMICON West 2022 and the Imec Roadmap

SEMICON West 2022 was held from July 12th to 14th at the Moscone Center in San Francisco.

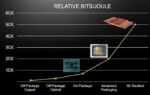

On Monday the 11th before the show, Imec held a technology forum at the Marriott Marquee right around the corner from the Moscone center. In recent years the Imec forums have shifted away from the process technology I cover to more of a system and… Read More

Imec Buried Power Rail and Backside Power Delivery at VLSI

At the VLSI Technology Symposium Imec presented on Buried Power Rails (BPR) and Backside Power Delivery (BSPD) in a paper entitled: “Scaled FinFETs Connected by Using Both Wafer Sides for Routing via Buried Power Rails”. I recently had a chance to interview one of the authors, Naoto Horiguchi about the work. I have interviewed … Read More

CMOS Forever?

Today, the CMOS chip manufacturing is the pinnacle of the human technology defining economy, society and perhaps us as modern humans. This was highlighted by the recent chip shortage, followed by the ‘shocking’ realization that more than 80% of all chips are manufactured in the Far East.

Important decisions need to be taken by … Read More