At IEDM 2023, Naoto Horiguchi presented on CFETs and Middle of Line integration. I had a chance to speak with Naoto about this work and this write up is based on his presentation at IEDM and our follow up discussion. I always enjoy talking to Naoto, he is one of the leaders in logic technology development, explains the technology in … Read More

Tag: hns

IEDM 2022 – Imec 4 Track Cell

At the IEDM conference in December 2022, Imec presented “Semi-damascene Integration of a 2-layer MOL VHV Scaling Booster to Enable 4-track Standard Cells,” I had a chance to not only read the paper and see it presented, but also to interview one of the authors Zsolt Tokie.

Logic designs are built up by standard cells such as inverters,… Read More

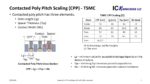

IEDM 2022 – TSMC 3nm

TSMC presented two papers on 3nm at the 2022 IEDM; “Critical Process features Enabling Aggressive Contacted Gate Pitch Scaling for 3nm CMOS Technology and Beyond” and “A 3nm CMOS FinFlexTM Platform Technology with Enhanced Power Efficiency and Performance for Mobile SOC and High Performance Computing Applications”.

When … Read More

SEMICON West 2022 and the Imec Roadmap

SEMICON West 2022 was held from July 12th to 14th at the Moscone Center in San Francisco.

On Monday the 11th before the show, Imec held a technology forum at the Marriott Marquee right around the corner from the Moscone center. In recent years the Imec forums have shifted away from the process technology I cover to more of a system and… Read More

Intel 2022 Investor Meeting

Last Thursday Intel held their investors meeting, in this write up I wanted to focus on my areas of coverage/expertise, process technology and manufacturing.

Technology Development presented by Ann Kelleher

Last year Intel presented their Intel Accelerated plan and, in this meeting, we got a review of where Intel stands on that… Read More

IBM at IEDM

IBM transferred their semiconductor manufacturing to GLOBALFOUNDRIES several years ago but still maintains a multibillion-dollar research facility at Albany Nanotech. IBM is very active at conferences such as IEDM and appears to have a good public relations department because they get a lot of press.

At the Litho Workshop … Read More

Intel Discusses Scaling Innovations at IEDM

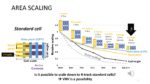

Standard Cell Scaling

Complex logic designs are built up from standard cells, in order to continue to scale logic we need to continually shrink the size of standard cells.

Figure 1 illustrates the dimensions of a standard cell.

Figure 1. Standard Cell Dimensions.

From figure 1 we can see that shrinking standard cell sizes requires… Read More

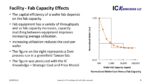

SISPAD – Cost Simulations to Enable PPAC Aware Technology Development

I was invited to give a plenary address at the SISPAD conference in September 2021. For anyone not familiar with SISPAD it is a premiere TCAD conference. This year for the first time SISPAD wanted to address cost and my talk was “Cost Simulations to Enable PPAC Aware Technology Development”.

For many years the standard in technology… Read More

VLSI Symposium – TSMC and Imec on Advanced Process and Devices Technology Toward 2nm

At the 2021 Symposium on VLSI Technology and Circuits in June a short course was held on “Advanced Process and Devices Technology Toward 2nm-CMOS and Emerging Memory”. In this article I will review the first two presentations covering leading edge logic devices. The two presentations are complementary and provide and excellent… Read More

ISS 2021 – Scotten W. Jones – Logic Leadership in the PPAC era

I was asked to give a talk at the 2021 ISS conference and the following is a write up of the talk.

The title of the talk is “Logic Leadership in the PPAC era”.

The talk is broken up into three main sections:

- Background information explaining PPAC and Standard Cells.

- A node-by-node comparisons of companies running leading edge logic