One of the benefits of using high-level synthesis is obviously the ease of writing some algorithms in SystemC since it is at a higher level than RTL (that’s why we call it high-level synthesis!). But a second benefit is at the verification level. Since a lot of the verification gets done at the SystemC level, less needs to be done at … Read More

Tag: hls

Xilinx’s Vivado HLS Will Float Your FPGA

Very rarely does the FPGA designer, especially with respect to RADAR, think of the FPGA as a floating point processor. Just to be sure I asked my 6 year old and she agreed. But you know what, the Xilinx FPGAs float. Go try it, order some up and fill up the tub.

Anyways I purpose a duel to the avid VHDL coder. I want you to design me a Sine(x) … Read More

Verifying Hardware at the C-level

As more people adopt high-level synthesis (HLS) they start to worry about what is the best design flow to be using. This is especially so for verification since it forms such a large part of the effort on a modern SoC. The more people rely on HLS for producing their RTL from C, the more they realize they had better do a good job of verifying… Read More

When Is a Good Time to Start Using High-Level Synthesis?

Of course if you are in the business of selling high-level synthesis (HLS) tools then the obvious answer is immediately. Start at 9am tomorrow morning. But a more realistic answer is when you are having to do something completely new. If you are working on a legacy design, perhaps with pre-existing IP, then moving the design up to … Read More

What Applications Implement Best with High Level Synthesis?

RTL coding using languages like Verilog and VHDL have been around since the 1980’s and for almost as long a time we’ve been hearing about High Level Synthesis, or HLS that allows an SoC designer to code above the RTL level where you code at the algorithm level. The most popular HLS languages today are C, C++ and SystemC.… Read More

Configurable System IP from a Tool Provider

While I have previously blogged on Forte’s Cynthesizer Workbench’s Interface Generator, I want to take another look from a different perspective. Watching the tool and IP together in action through public videos provided by Forte it struck me as odd what I did not consider earlier, on what should have been obvious to me – Forte is… Read More

Analysis of HLS Results Made Easier

In a recent article I discussed how easy it was to debug SystemC source code as shown in a video published on YouTube by Forte Design Systems. I also commented on the usefulness of the well-produced Forte video series. Today, I am reviewing another video in that series on analyzing high-level synthesis (HLS) results.

Cynthesizer… Read More

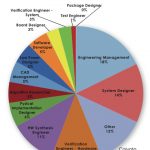

Calypto 2013 Report

Each year Calypto runs a survey of end-users. This year’s survey and report has two parts, power reduction and high level synthesis (HLS).

The topics covered are:

- survey methodology and demographics

- top methods used to reduce power

- engineering time spent on specfiic RTL tasks to reduce power

- plans to deploy RTL power reduction

Interview with Forte CTO John Sanguinetti on Cynthesizer 5

Recently, Forte Design Systems announced the release of a new core engine to their popular high-level synthesis tool offering. It is a large undertaking, so I asked John Sanguinetti, Forte’s CTO, to answer some questions about that development effort.

Q. How long has it been since the last major upgrade of the Cynthesizer… Read More

Calypto, in Three Part Harmony

As Julius Caesar said, “Gallia est omnis divisa in partes tres.” All Gaul is divided into 3 parts. Calypto is similar with three product lines that work together to provide a system level approach to SoC design. Two of those product lines are not unique, in the sense that similar capabilities are available from a handful… Read More