Can I ask you a personal question dear reader? It is only fair, you know so much about me and all, so here goes… Why are you still hand coding you’re FPGA design? Surely you are not hand coding interfaces, like PCie, SRIO, DDR, GbE, JESD204B, HMC etc… Correct? OK, why then are you still hand coding the guts of the world’s best, super-duper… Read More

Tag: hls

Xilinx and Red Pitaya is Tootie Fruity

Xilinx’s Zynq SoC is the best selling FPGA of all time. Zynq has brought together, at first an uncomfortable but necessary mix of software and hardware engineers. Two very different but special kind of people. Me, I’m of the hardware persuasion. Zynq is the start of the much needed open FPGA community. This will drive down the price… Read More

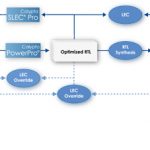

Calypto: the View From the Top

At DVCon today I talked to Sanjiv Kaul, the CEO of Calypto. Just as a reminder, Calypto have 3 products, SLEC (sequential logical equivalence checking, also called sequential formal verification), PowerPro (sequential RTL level power reduction) and Catapult High Level Synthesis (that they took over from Mentor in 2011 in a complicated… Read More

Carbon Design Systems – Secret of Success

Last week, after learning from the press releaseof Carbonabout its rocking sustained growth with record-breaking revenue and a thumping 46% increase in bookings, I was interested to know some more details about what drives Carbon to such an amazing performance in an EDA market that is generally prone to growth of a few percentage… Read More

Happy Birthday Xilinx

I have never done this before, wished a company happy birthday. So here goes, Happy Birthday Xilinx! How does it feel to be 30? Looking good eh? Signing up for AARP? My family and I just sang and had cake and ice cream. They did look at me like I was nuts when I set a place at the table for a Xilinx FPGA. In all seriousness, over the years Xilinx… Read More

Cadence Acquires Forte

Cadence today announced that it is acquiring Forte Design Systems. Forte was the earliest of the high-level synthesis (HLS) companies. There were earlier products. Synopsys had Behavioral Compiler and Cadence had a product whose name I forget (Visual Architect?), but both products were too early and were canceled. Cadence … Read More

Xilinx’s Mixed Signal FPGA

Something in all the Xilinx chatter of UltraScale 20nm, 16nm, having massive amounts of Gigabit transceivers, DSP blocks, RAM, HLS, Rapid Design Closure gets lost… and that is Xilinx’s ability for Mixed Signals. I do not mean when you are talking with the wife (Remember Listen!), but a wonderful block that lives within… Read More

SLEC is Not LEC

One of the questions that Calypto is asked all the time is what is the difference between sequential logical equivalence checking (SLEC) and logical equivalence checking (LEC).

LEC is the type of equivalence checking that has been around for 20 years, although like all EDA technologies gradually getting more powerful. LEC is … Read More

Xilinx Pulls Back the 20nm UltraScale Curtain

This week Xilinx has announced that “The Xilinx 20nm All Programmable UltraScale™ portfolio is now available with detailed device tables, product documentation, design tools and methodology support.”

Do you know what 20nm is? It’s small, tiny. Think about it this way, as I just learned today that one nanometer is about as long… Read More

Addressing Power at Architectural and RTL Levels

Major power reductions are possible by reducing power at the RTL and system levels, and not just at the gate and physical level. In fact, as is so often the case in design, changes can have much more impact when done at the higher level, even given that at that point in the design there is less accurate feedback about changes. Later the… Read More