You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

On Friday April 12th Intel held a press briefing on their adoption of High NA EUV with Intel fellow and director of lithography Mark Phillips.

In 1976 Intel built Fab 4 in Oregon, the first Intel fab outside of California. With the introduction of 300mm Oregon became the only development site for Intel with large manufacturing, development,… Read More

On Wednesday, February 21st Intel held their first Foundry Direct Connect event. The event had both public and NDA sessions, and I was in both. In this article I will summarize what I learned (that is not covered by NDA) about Intel’s business, process, and wafer fab plans (my focus is process technology and wafer fabs).

Business

…

Read More

At SEMICON West I had a chance to catch up with Mike Lercel of ASML. In this article I am going to combine ASML presentation material from the SPIE Advanced Lithography Conference, Mike’s SEMICON presentation, my discussions with Mike at SEMICON and a few items from ASML’s recent earnings call.

DUV

ASML continues to improve DUV systems.… Read More

The SPIE Advanced Lithography Conference was held in February. I recently had the opportunity to interview Steven Scheer, vice president of advanced patterning process and materials at imec and review selected papers that imec presented.

I asked Steve what the overarching message was at SPIE this year, he said readiness for … Read More

-Demand far exceeds supply & much longer than any downturn

-Full speed ahead-$40B in solid backlog provides great comfort

-ASP increase shows strength- China is non issue

-In a completely different league than other equipment makers

Reports a good beat & Guide

Revenues were Euro6.4B with system sales making up Euro4.7B… Read More

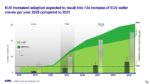

At the 2022 SPIE Advanced Lithography Conference, ASML presented an update on EUV. I recently had a chance to go over the presentations with Mike Lercel of ASML. The following is a summary of our discussions.

0.33 NA

The 0.33 NA EUV systems are the production workhorse systems for leading edge lithography today. 0.33 NA systems are… Read More

Too much demand- A “good” problem-Managing supply & capacity-Intel & Hi NA

–ASML great Q4 results-Demand off charts-Supply constrained

-Dealing with chain issues, putting out fires, expediting

-Looking forward to next gen High NA in 2024/2025

-Intel’s order doesn’t give advantage,… Read More

I couldn’t attend the SPIE Advanced Lithography Conference this year for personal reasons, but last week Mike Lercel of ASML was nice enough to walk me through the major ASML presentations from the conference.

Introduction

In late 2018, Samsung and TSMC introduced 7nm foundry logic processes with 5 to 7 EUV layers, throughout … Read More