Walking across a carpet can generate up to 35,000 volts of static charge, which is tens of thousands of times higher than the operating voltages of most integrated circuits. When charge build up from static electricity is exposed to the pins of an IC, the electrostatic discharge (ESD) protection network on the chip is intended to… Read More

Tag: hbm

Adding CDM Protection to a Real World LNA Test Case

In RF designs Low Noise Amplifiers (LNA) play a critical role in system operation. They simultaneously need to be extremely sensitive and noise free, yet also must be able to withstand strong signal input without distortion. LNA designers often struggle to meet device performance specifications. Their task is further complicated… Read More

Upcoming HBM and CDM ESD Verification Seminar in Taiwan

The electrostatic discharge that occurs in lightening, as seen in the picture below, can cause serious damage to the objects on the ground. Over centuries mankind has devised ways, such as lighting rods and arresters, to deflect the energy so it is dissipated harmlessly. The same drama plays out on modern semiconductors due to … Read More

A Practical Approach to Modeling ESD Protection Devices for Circuit Simulation

Lurking inside of every Mosfet is a parasitic bipolar junction transistor (BJT). Of course, in normal circuit operation the BJT does not play a role in the device operation. Accordingly, SPICE models for Mosfets do not behave well when the BJT is triggered. However, these models work just fine for most purposes. The one important… Read More

TSMC Q3 2018 Earnings Call Discussion!

The TSMC OIP Forum was very upbeat this year and now we know why. It wasn’t long ago that some media outlets and a competitor said 7nm would not be a popular node because it is too expensive blah blah blah. People inside the fabless semiconductor ecosystem however know otherwise. As I have said before, 7nm will be another strong node … Read More

Does the G in GDDR6 stand for Goldilocks?

In the wake of TSMC’s recent Open Innovation Platform event, I spoke to Frank Ferro, Senior Director of Product Management at Rambus. His presentation on advanced memory interfaces for high-performance systems helped to shed some light on the evolution of system memory for leading edge applications. System implementers now… Read More

Machine Learning Drives Transformation of Semiconductor Design

Machine learning is transforming how information processing works and what it can accomplish. The push to design hardware and networks to support machine learning applications is affecting every aspect of the semiconductor industry. In a video recently published by Synopsys, Navraj Nandra, Sr. Director of Marketing, takes… Read More

Webinar Alert: High Bandwidth Memory ASIC SiPs for HPC and Networking Applications

Calling all ASIC designers working on High-Bandwidth Memory (HBM) access architectures in high-performance computing (HPC), networking, deep learning, virtual reality, gaming, cloud computing and data center applications. You won’t want to miss this upcoming webinar focused on system integration aspects of a HBM2 ASIC… Read More

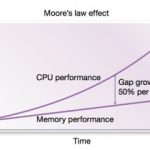

HBM offers SOC’s dense and fast memory options

Dual in-line memory modules (DIMM’s ) with double data rate synchronous dynamic random access memory (DDR SDRAM) have been around since before we were worried about Y2K. Over the intervening years this format for provisioning memory has evolved from supporting DDR around 1995, to DDR1 in 2000, DDR2 in 2003, DDR4 in 2007 and DDR4… Read More

Memories for the Internet

In 1969 the Internet was born at UCLA when a computer there sent a message to a computer at Stanford. By 1975, there were 57 computers on the ‘internet’. Interestingly in the early seventies I actually used the original Xerox Sigma 7 connected to the internet in Boelter Hall at UCLA. A similar vintage computer is now in this room commemorating… Read More