You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

– We just finished the most happy SEMICON West in a long time

– IMEC stole the show- HBM has more impact than size dictates

– Has Samsung lost its memory mojo? Is SK the new leader?

– AI brings new tech issues with it – TSMC is still industry King

Report from SEMICON West

The crowds at Semicon West were both… Read More

Introduction of 2.5D and 3D multi-die based products are helping extend the boundaries of Moore’s Law, overcoming limitations in speed and capacity for high-end computational tasks. In spite of its critical function within the 3DIC paradigm, the interposer die’s role and related challenges are often neither fully comprehended… Read More

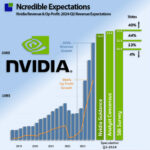

This article previews Nvidia’s earnings release and will be updated during and after the earnings release. As usual, we will compare and contrast the Nvidia earnings with our supply chain glasses to identify changes and derive insights. Please return to this article, as it will be updated over the next week as we progress with our… Read More

We are in the semiconductor market phase where everybody disagrees on what is going on. The market is up; the market is down. Mobile phones are up…. oh no, now they are down. The PC market is up—oh no, we need to wait until we can get an AI PC. The inflation is high—the consumer is not buying.

For us in the industry, the 13-week financial … Read More

– Lam reports another flat quarter & guide- No recovery in sight yet

– Seems like no expectation of recovery until 2025- Mixed results

– DRAM good- NAND weak- Foundry/Logic mixed-Mature weakening

– Clearly disappointing to investors & stock hoping for a chip recovery

Another Flat Quarter &

…

Read More

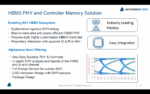

GenAI, the most talked-about manifestation of AI these days, imposes two tough constraints on a hardware platform. First, it demands massive memory to serve large language model with billions of parameters. Feasible in principle for a processor plus big DRAM off-chip and perhaps for some inference applications but too slow … Read More

MosChip is a publicly traded company founded in the year 1999, they offer semiconductor design services, turnkey ASIC, software services, and end-to-end product engineering solutions. The company headquartered in Hyderabad, India, with five design centers and over 1300 engineers located in Silicon Valley (USA), Hyderabad,… Read More

In the technology realm of artificial intelligence (AI) and high-performance computing (HPC), the demand for higher throughput and efficiency has never been greater. To meet these evolving demands, innovative memory solutions have emerged as critical enablers, paving the way for transformative advancements in computing… Read More

– AMAT slightly better than expected, flat & guides flat but > expected

– Expects better 2024- Systems flat, service up, display down

– China risk remains high at 45%- $200M Sculpta expected in 2024

– HBM 5% of industry but not a lot of tool sales- but high growth

Still bumping along with flattish … Read More

– Lam reported as expected and guided flat- No recovery yet

– Some mix shifts but China still 40% (8X US at 5%)-NVM still low

– HBM is promising but Lam needs a broad memory recovery

– Lam has not seen order surge ASML saw- Likely lagging by 3-4 QTRs

An in line quarter and uninspiring flat guide for Q1

As compared… Read More