Using chiplets is an emerging trend well-covered at #62DAC and they even had a dedicated Chiplet Pavilion, so I checked out the presentation from Dan Slocombe, Design Engineering Architect in the Compute Solutions Group at Cadence. In a short 20 minutes Dan managed to cover a lot of ground, so this blog will summarize the key points.… Read More

Tag: genus

IoT Designs Beginning to Shift to 7nm: Promises Upside for Cadence Physically-Aware Design Flow

Until recently, ICs at bleeding edge nodes like 7nm technology from foundries like TSMC were mostly targeted for high-performance-computing (HPC) and mobile applications or possibly high radix switches that needed the increased performance of advanced nodes. The momentum of Moore’s law and Moore-than-Moore saw foundries… Read More

Digital Design Trends – A Cadence Perspective

I talked with Paul Cunningham (VP front-end digital R&D) at CDNLive recently to get a Cadence perspective on digital design trends. He sees needs from traditional semiconductor companies evolving as usual, with disruption here and there from consolidation. But on the system side there is explosion in demand – for wearables,… Read More

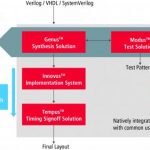

Cadence Adds New Dimension to SoC Test Solution

It requires lateral thinking in bringing new innovation into conventional solutions to age-old hard problems. While the core logic design has evolved adding multiple functionalities onto a chip, now called SoC, the structural composition of DFT (Design for Testability) has remained more or less same based on XOR-based compression… Read More

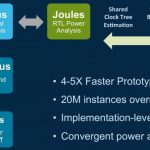

A New Unified Power Solution at All Levels

When situation demands, multiple solutions appear with a slight lag of time. Similar is the story with estimating and optimizing power at SoC level. In the SoC era, power has become a critical criterion long ago, and there are tools available for power analysis and optimization. However, with more mobile and IoT (Internet of Things)… Read More

Eyes Meet Innovations at DAC

It gives me a very nice, somewhat nostalgic, feeling after attending the 52[SUP]nd[/SUP] DAC. There was a period during my final academic year in 1990 and my first job when I used to search through good technical papers in DAC proceedings and try implementing those concepts in my project work. In general, representation from ‘R&D… Read More

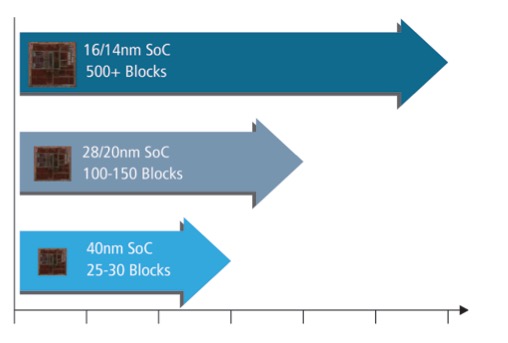

Logic Synthesis Reborn

Combine the pressures of Moore’s Law which enable billion transistor SoCs and the shortened time to market from consumer electronics product cycles and you have the perfect storm for EDA tool vendors. A modern SoC can have 500 or more blocks, creating both a design and verification challenge. How in the world do you write … Read More