You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

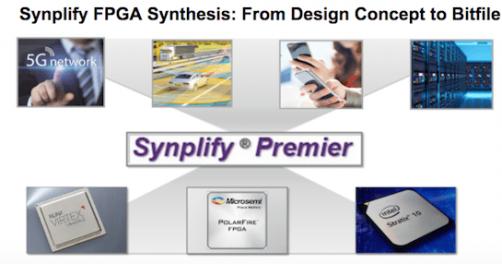

You might wonder why, in FPGA design, you would go beyond simply using the design tools provided by the FPGA vendor (e.g. Xilinx, Intel/Altera and Microsemi). After all, they know their hardware platform better than anyone else, and they’re pretty good at design software too. But there’s one thing none of these providers want to… Read More

According to a recent engineering survey, completing IC designs on time and within specifications gets exponentially more challenging with each node. Why? Here are the top five reasons:… Read More

Many tools find clock domain crossings (CDCs) in FPGA designs. Some don’t find the right ones since they don’t comprehend things like in-house synchronizer constructs. Some find too many based on misunderstanding intent, inaccurate constraints, and other factors that lead to noise.… Read More

Digital outputs can either go ON or OFF. Analog signals, on the other side, can smoothly assume multiple values in a range. There is a technique that emulates analog behavior with a digital output. That technique is PWM, namely, Pulse Width Modulation. It can be implemented as pulses with varying ‘high’ and ‘low’… Read More

Men marry women wishing they will never change, but they do.Women marry men wishing they will be able to change them, but they don’t.

When I was young, even during my University studies, I was a real disaster in anything related to order. My room was always a mess. Whenever my mother or any other would try to change my ways (even… Read More

On the first two chapters of this Tutorial we started with a simple LFSR module and added a test bench. Then, on chapters three and four we upgraded our module with some features and learned to export the test bench data to files.

… Read More

In the first part of this tutorialwe started with a simple implementation of an LFSR block (Chapter 1) and its test bench (Chapter 2). Let’s make our code look a bit more professional.

… Read More

In this tutorial we will see how to design a VHDL block. We will start with a very simple block and we will gradually add features to it. We will also simulate it and test its output with Matlab. Over the process we will see:

… Read More

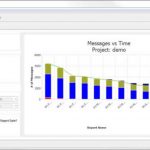

You’re an RTL pro. You know what’s inside your code, and how many bugs you’ve tracked down and exterminated along the development path, and how much work remains. So, why did the meeting notice that just popped up asking for a monthly management project review presentation ruin your day?… Read More