You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

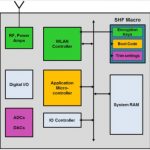

Virtually all SoCs require one-time programmable (OTP) memory. Each SoC is different, of course, but two main uses are large memories for holding boot and programming code and small memories for holding encryption keys and trimming parameters, such as radio tuning information and so on.

There are alternatives to putting an OTP… Read More

The existence of TSMC’s Open Innovation Platform (OIP) program further sped up disaggregation of the semiconductor supply chain. Partly, this was enabled by the existence of a healthy EDA industry and an increasingly healthy IP industry. As chip designs had grown more complex and entered the system-on-chip (SoC) era, the amount… Read More

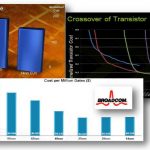

It is beginning to look as if 28nm transistors, which are the cheapest per million gates compared to any earlier process such as 45nm, may also be the cheapest per million gates compared to any later process such as 20nm.

What we know so far: FinFET seems to be difficult technology because of the 3D structure and so the novel manufacturing… Read More

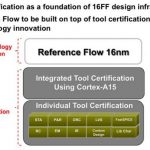

Today TSMC announced three reference flows that they have been working on along with various EDA vendors (and ARM and perhaps other IP suppliers). The three new flows are:

- 16FinFET Digital Reference Flow. Obviously this has full support for non-planar FinFET transistors including extraction, quantized pitch placement, low-vdd

…

Read More

Last week I heard about the Indian Cabinet approving the proposal for setting up of two Fabs in India. One led by IBM, Tower Jazzand JP Associates(an Indian business house), and the other led by HSMC(Hindustan Semiconductor Manufacturing Co.), ST Microelectronicsand Silterra. Indian Semiconductor community including IESA… Read More

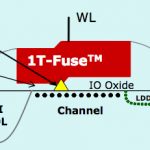

I’ve written before about the basic capabilities of Sidense’s single transistor one-time programmable memory products (1T-OTP). Just to summarize, it is an anti-fuse device that works by permanently rupturing the gate oxide under the bit-cells storage transistor, something that is obviously irreversible.… Read More

At IDF Brian Krzanich gave the keynote. I won’t summarize the whole thing here but just talk about one part that was something they had actually managed to keep secret ahead of time: Quark.

Quark is a synthesizable core. It uses 1/10th power of Atom and is 1/5 size. Now I am writing this, I don’t know if this is a fair comparison… Read More

GlobalFoundries has been in Singapore for a long time. Longer than GlobalFoundries has existed in fact. Chartered Semiconductor was started in Singapore in 1987 and GF acquired them in early 2010 less than a year after they were created by spinning out the manufacturing arm of AMD. When GF was started their state of the art fab was… Read More

At TSMC’s OIP on October 1st, Mentor Graphics have 5 different presentations. Collect the whole set!

11am, EDA track. Design Reliability with Calibre Smartfill and PERC. Muni Mohan of Broadcom and Jeff Wilson of Mentor. New methodologies were invented for 28nm for smart fill meeting DFM requirements (and at 20nm me may … Read More

Almost without exception these days, semiconductor products face strict power and thermal budgets. Of course there are many issues with dynamic power but one big area that has been getting increasingly problematic is static power. For various technical reasons we can no longer reduce the voltage as much as we would like from one… Read More