Atrenta’s SoC realization seminars, “Fast Track Your SoC Design” have started.The first one was in Ottowa last Tuesday, and it was a full house. In a straw poll, most of the attendees acknowledged facing IP handoff and quality issues. The keynote speaker was Dr Yuejian Wu, director of ASIC development at Infinera… Read More

Tag: eda

Hardware Configuration Management approach awarded a Patent

Hardware designers use complex EDA tool flows that have collections of underlying binary and text files. Keeping track of the versions of your IC design can be a real issue when your projects use teams of engineers. ClioSoft has been offering HCM (Hardware Configuration Management) tools that work in the most popular flows of: … Read More

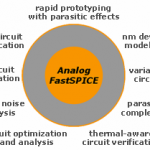

When analog/RF/mixed-signal IC design meets nanometer CMOS geometries!

In working with TSMC and GlobalFoundries on AMS design reference flows I have experienced first hand the increasing verification challenges of nanometer analog, RF, and mixed-signal circuits. Tools in this area have to be both silicon accurate and blindingly fast! Berkeley Design Automation is one of the key vendors in this … Read More

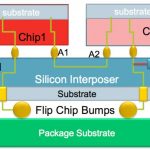

2.5D and 3D designs

Going up! Power and performance issues, along with manufacturing yield issues, limit how much bigger chips can get in two dimensions. That, and the fact that you can’t manufacture two different processes on the same wafer, mean that we are going up into the third dimension.

The simplest way is what is called package-in-package… Read More

Nanometer Circuit Verification Forum

Verifying circuits on advanced process nodes has always been difficult, and it’s no easier with today’s nanometer CMOS processes. There’s a great paradox in nanometer circuit design and verification. Designers achieve their greatest differentiation when they implement analog, mixed-signal, RF and custom … Read More

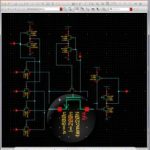

Transistor Level IC Design?

If you are doing transistor-level IC design then you’ve probably come up against questions like:

- What Changed in this schematic sheet?

- How did my IC layout change since last week?

In the old days we would hold up the old and new versions of the schematics or IC layout and try to eye-ball what had changed. Now we have an automated… Read More

Third Generation DFM Flow: GLOBALFOUNDRIES and Mentor Graphics

Introduction

Mentor Graphics and GLOBALFOUNDRIES have been working together for several generations since the 65nm node on making IC designs yield higher. Michael Buehler-Garcia, director of Calibre Design SolutionsMarketing at Mentor Graphics spoke with me by phone today to explain how they are working with GLOBALFOUNDRIES… Read More

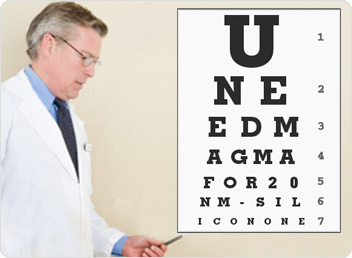

20nm SoC Design

There are a large number of challenges at 20nm that didn’t exist at 45nm or even 32nm.

The biggest issues are in the lithography area. Until now it has been possible to make a reticle using advanced reticle enhacement technology (RET) decoration and have it print. Amazing when you think that at 45nm we are making 45nm features… Read More

Fast Track your SoC Design

Atrenta has four seminars coming up on SoC realization. More and more design is actually about finding IP and integrating it together at the block level, and then handing it off to a standard RTL to GDSII flow. The three focus areas are:

- finding quality IP faster

- accelerating IP integration and SoC assembly

- handing off RTL successfully.

ANSYS Regional Conference

Next Tuesday, August 23rd, is the ANSYS Regional Conference for Silicon Valley. It takes place at the Techmart Network Meeting Center. Apache has three presentations during the day:

- 9.25-9.45 Andrew Yang Introducing Apache Design Solutions

- 11.00-11.30 Methodology for delivering power-efficient designs from concept to