My new iPad lasts about 10 hours on a single charge and the A5X processor is designed with a 45nm process from Samsung. Processor chips for tablets like this use a multi-voltage IC design flow to reduce total power by:… Read More

Tag: eda

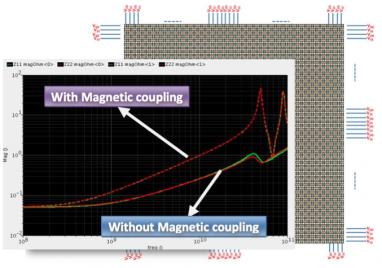

Power Integrity Challenges for High Speed and High Frequency Designs

There is an interesting discussion on the LinkedIn SoC Power Integrity Group in regards to the power integrity challenges for high speed and high frequency designs. More specifically, the additional attention an on-chip power delivery network (PDN) requires as the operating frequency of ICs and SoCs increases.

The PDN has to… Read More

Advanced Node Design Webinar Series

At advanced process nodes, variation and its effects on the design become a huge challenge. Join Cadence® Virtuoso® experts for a series of technical webinars on variation-aware design. Learn how to use advanced technologies and tools to analyze and understand the affects of variation. We’ll introduce you to the latest Virtuoso… Read More

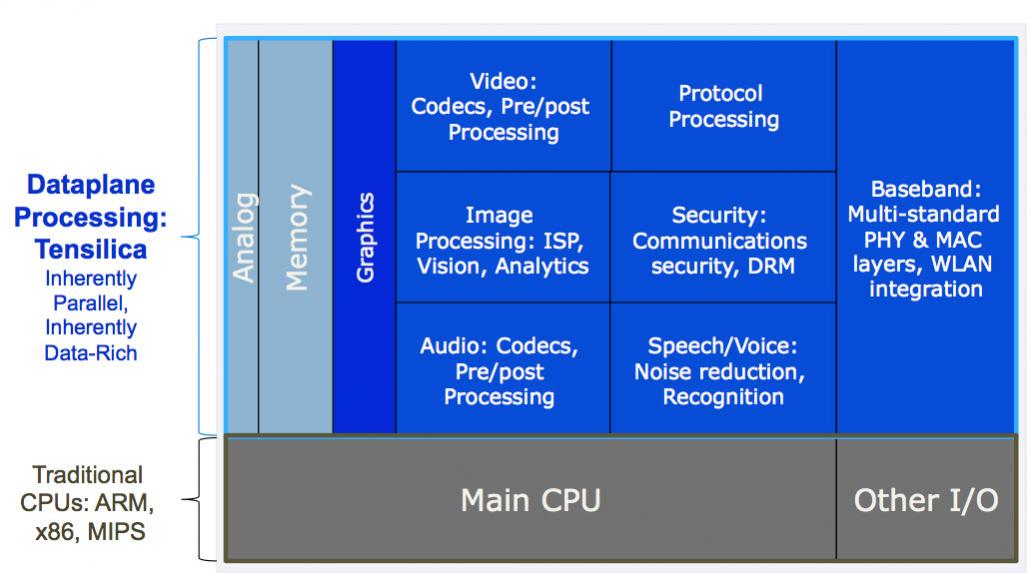

The Protocol Processing Dataplane

At the Linley processor conference this week, Chris Rowen, the CTO of Tensilica presented on the protocol processing dataplane. That sounds superficially like he is talking about networking but in fact true protocol processing is just part of adding powerful compute features to the dataplane. Other applications are video, … Read More

ICCAD: 30 years

ICCAD is November 5th to 8th in the Hilton San Jose (downtown).

It is very off topic, but if you are British then November 5th is the rough equivalent of July 4th when there are fireworks displays all over the country. Britain is one of very few countries that transitioned from some sort of autocracy to a democracy without having a revolution.… Read More

Soft IP Quality Standards

As SoC design has transformed from being about writing RTL and more towards IP assembly, the issue of IP quality has become increasingly important. In 2011 TSMC and Atrenta launched the soft IP qualification program. Since then, 13 partners have joined the program.

IP quality is multi-faceted but at the most basic level, an IP block… Read More

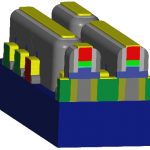

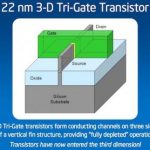

Designing with FinFETs

Intel is the number one semiconductor company in the world and has taken the lead in bringing FinFET (aka Tri-Gate) silicon to market at the 22nm node starting in May 2011, so now we see the pure play foundries playing catch-up and start talking about their own FinFET roadmaps. IC designers and layout engineers want to know how their… Read More

Apache Dimensions of Electronic Design Seminars

Coming up are ANSYS/Apache seminars on Dimensions of Electronic Design. Watch the video where Arvind Shanmugavel gives some details about why you should attend. Probably most readers are in Silicon Valley, and the seminar here is on 18th at the Hyatt (next to Santa Clara convention center).

The seminars are free to qualified attendees.… Read More

Design Automation Conference 2013 Austin, Texas Call for Papers!

DAC’s technical program offers the best-in-class solutions that promise to advance Electronic Design Automation (EDA) and Embedded Systems and Software (ESS). DAC 2013 is seeking submissions that deal with design technologies and algorithms, addressing all aspects of electronic design across several submission categories.… Read More

Exclusive Sneak Peek: Cadence at TSMC OIP Ecosystem Forum 2012

The TSMC Open Innovation Platform® (OIP) Ecosystem Forum brings TSMC’s design ecosystem member companies together to share with our customers real-case solutions for customers’ design challenges and success stories of best practice in TSMC’s design ecosystem. More than 90% of the attendees last year said “this… Read More