At the DAC 50th anniversary banquet, Pat Pistilli won the award for most tenacious attendee, having been to all 50 DACs. Well, and for creating DAC and sustaining it. He was general chair for the first DAC (not yet called DAC) and, of course, would eventually form MP Associates with his wife Marie, which still runs DAC today. In 2010… Read More

Tag: eda

Agilent ADS Users, Find Out About Design Data Management

In May, ClioSoft and Agilent announced that Agilent’s Advanced Design System (ADS) was now integrated with ClioSoft’s SOS Design Data Management. I interviewed Greg Peterschmidt of Agilent at that time. The information page for the combined product, known as SOS viaADS is here.

Next week ClioSoft is presenting… Read More

DAC by the Numbers

The attendance numbers for DAC are out. Unless you have been living under a stone you know that DAC was in Austin Texas a couple of weeks ago. Attendance was:

- full conference passes: 1589

- exhibits-only passes: 2364

- booth staff: 1998

The registration is slightly lower than last year when DAC was in San Francisco (as it will be again … Read More

What does 3D IC, FinFETs, and EUV have in common?

They are three of the top trending terms on SemiWiki and three of the hot topics at this year’s Semicon West:

In its 43rd year, SEMICON West is the flagship annual event for the global microelectronics industry. It is the premier event for the display of new products and technologies for microelectronics design and manufacturing,… Read More

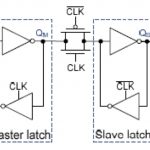

Is Your Synchronizer Doing its Job (Part 1)?

Recently, I discussed the increasing risk of metastability hazards at nanoscale geometries. These risks are significantly aggravated at low supply voltages and low temperatures and must be addressed during the design cycle of any mission critical application. This time I discuss what it takes to estimate a synchronizer’s … Read More

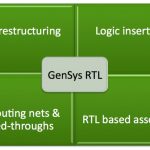

Derivative Designs Need Tools Too

Increasingly, SoC designs consist of assembling blocks of pre-designed IP. One special case is the derivative design where not just the IP blocks get re-used but a lot of the assembly itself. For example, in the design below some blocks are added, some blocks are updated, some hierarchy is changed. But the bulk of the design remains… Read More

Increasing Automotive Semiconductor Test Quality

The growing amount of electronics within today’s automobiles is driving very high quality and reliability requirements to a widening range of semiconductor devices. At the same time, traditional fault models are becoming less effective at achieving desired silicon quality levels. Improvements in test solutions are needed… Read More

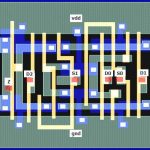

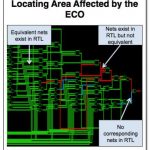

Formality Ultra, Streamline Your ECOs

One of the most challenging stages in an SoC design is achieving timing closure. Actually design closure is perhaps a better term since everything needs to come together such as clock tree, power nets, power budget and so on. Changes made to the design are known as ECOs (which stands for engineering change orders, a term that comes… Read More

Should You Buy All Aspects of Your IP From a Single Supplier?

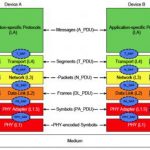

Interface IP typically consists of multiple layers, most importantly a PHY (level 1) analog (or mixed signal) block that handles the interface to the outside world and a number of levels of digital controllers. The interfaces between all these levels, especially between the PHY and the controller, is often defined by the interface… Read More

Swap and Play Extended To Chip Fabric and Memory Controllers

Virtual platforms enable software development to take place on a model of an electronic system. What everyone would like is models that are fast and accurate but that is simply not possible. Fast models are fast because they don’t model everything at the signal level. And accurate models get to be accurate by handling a lot of detail… Read More