As a blogger in the EDA industry I get to write every week, however I also end up reading every blog on SemiWiki plus multiple other sites to keep current on what’s happening in our business. I thought that it would be informative to look at Cadence Design Systems and how they are using blogging to talk not just about their own EDA… Read More

Tag: eda

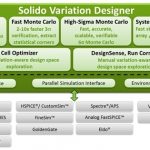

Process Variation is a Yield Killer!

With the insatiable wafer appetites of the fabless semiconductor companies in the mobile space, yield has never been more critical. The result being better EDA tools every year and this blog highlights one of the many examples. It has been a pleasure writing about Solido Design Automation and seeing them succeed amongst the foundries… Read More

A Brief History of TSMC’s OIP part 2

The existence of TSMC’s Open Innovation Platform (OIP) program further sped up disaggregation of the semiconductor supply chain. Partly, this was enabled by the existence of a healthy EDA industry and an increasingly healthy IP industry. As chip designs had grown more complex and entered the system-on-chip (SoC) era, the amount… Read More

Early Test –> Less Expensive, Better Health, Faster Closure

I am talking about the health of electronic and semiconductor design, which if made sound at RTL stage, can set it right for the rest of the design cycle for faster closure and also at lesser cost. Last week was the week of ITC(International Test Conference) for the Semiconductor and EDA community. I was looking forward to what ITC… Read More

Mentor Teaches Us About the Higg’s Boson

Once a year Mentor has a customer appreciation event in Silicon Valley with a guest speaker on some aspect of science. This is silicon valley, after all, so we all have to be geeks. This year it was Dr Sean Carroll from CalTech on The Particle at the End of the Universe, the Hunt for The Higg’s Boson and What’s Next.

Wally … Read More

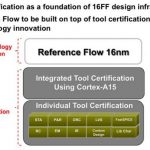

TSMC’s 16FinFET and 3D IC Reference Flows

Today TSMC announced three reference flows that they have been working on along with various EDA vendors (and ARM and perhaps other IP suppliers). The three new flows are:

- 16FinFET Digital Reference Flow. Obviously this has full support for non-planar FinFET transistors including extraction, quantized pitch placement, low-vdd

How to Design an LTE Modem

Designing an LTE modem is an interesting case study in architectural and system level design because it is pretty much on the limit of what is possible in a current process node such as 28nm. I talked to Johannes Stahl of Synopsys about how you would accomplish this with the Synopsys suite of system level tools. He is the first to admit… Read More

Back To The Future: 50th Anniversary of EDA

October 16[SUP]th[/SUP] at the Computer History Museum, EDAC is hosting EDA: Back to the Future to celebrate 50 years of EDA. EDAC always has a fall event of some sort and historically it has been the Kaufman Award Dinner. This year, the Kaufman Award was presented (to Chenming Hu) at 50[SUP]th[/SUP] DAC, so the fall EDAC calendar… Read More

Emerging Trend – Choose DRAM as per Your Design Need

Lately I was studying about new innovations in memory world such as ReRAM and Memristor. As DRAM (although it has become a commodity) has found its extensive use in mobile, PC, tablet and so on, that was an inclination too to know more about. While reviewing Cadence’s offering in memory subsystems, I came across this whitepaperwhich… Read More

TSMC OIP: Mentor’s 5 Presentations

At TSMC’s OIP on October 1st, Mentor Graphics have 5 different presentations. Collect the whole set!

11am, EDA track. Design Reliability with Calibre Smartfill and PERC. Muni Mohan of Broadcom and Jeff Wilson of Mentor. New methodologies were invented for 28nm for smart fill meeting DFM requirements (and at 20nm me may … Read More