In the wake of increased global competitiveness and shorter time-to-market windows, there has been a renewed focus by design management on the underlying data management infrastructure of the design teams. An increasing number of systems-on-chip (SoCs) now have some type of analog, digital and/or RF modules, making it imperative… Read More

Tag: eda

The Fine Art of Engineering

There’s a small art gallery near the office. It features a new set of paintings by a local artist every two weeks. As I walk by I tend to check out what’s hanging in there. Sometimes I turn up my nose at what I see – a bit too wacky, a bit too abstract, a bit too paint by numbers. Sometimes I walk in to take a closer look but leave the shop empty-handed… Read More

Synopsys on the Future of Custom Layout!

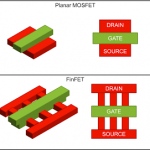

Analog and mixed signal design has received more than their fair share of attention since the mobile revolution and now that FinFETs are in production at the foundries I see that trend continuing. As a result this year there are some interesting things brewing in EDA, especially in the area of Custom Layout.

Innovation in Custom … Read More

IP Development in Japan

As semiconductor IP is growing bigger in size and more complex in providing complete solution for a particular functionality in an SoC, regions from across the world are joining to provide various types of services in the overall value-chain of IP development, verification, and its integration into SoCs. … Read More

EDA and the Big Short!

A funny thing happened while I was reading “The Big Short: Inside the Doomsday Machine”. The book explains the subprime mortgage crisis in painful detail by profiling several key players who predicted and profited from the bubble pop. As a home owner and faux slumlord I had a front row seat to this horror show so it was an interesting… Read More

2015 3D ASIP conference: Thar’s Gold in Them Thar Hills!

Last week I presented at the 3D ASIP EDA Tutorial and attended the Conference. In previous years, leading edge papers were presented from large companies pushing a solution to meet their needs. These companies had the resources and clout to achieve some astounding successes, but the lingering question was: “what other product… Read More

Calibre in the Middle of Semiconductor Ecosystem

Albert Einsteinhad said, “In the middle of difficulty lies opportunity”. In today’s world dominated by technology, or I must say internet which has initiated collaborative information sharing, “leading from the middle” is the new mantra of life.… Read More

2016 EDA Dead Pool

The most commonly asked question during conference calls with Wall Street of late is in regards to the massive consolidation the semiconductor industry is experiencing. How will the consolidation affect the Foundries? How will the consolidation affect EDA and IP? How will the consolidation affect the semiconductor industry… Read More

Merger Mania: The Future of the Semiconductor Industry

In a semiconductor industry which appears maturing, we are also seeing the technologies unravelling newer transistor structures, memories, processors, and newer ways of designing ICs and electronic systems. The present decade appears to be at the cusp of a new transformation in the semiconductor industry. Amid a slew of mergers… Read More

Verification with Tcl for what? – part 2

In Orion Bytes we use Tcl both for the internal research, product and different verification services. We use also SystemVerilog UVM and Python based Cocotb for different approaches. I think it’s no need to deep into the SystemVerilog and UVM principles here – today’s main verification fashion is well described through… Read More