When I posted earlier on Qualcomm presenting with ANSYS on differential energy analysis, I assumed this was just the usual story on RTL power estimation being more accurate for relative estimation between different implementations. I sold them short. This turned out to be a much more interesting methodology for optimizing total… Read More

Tag: dynamic power

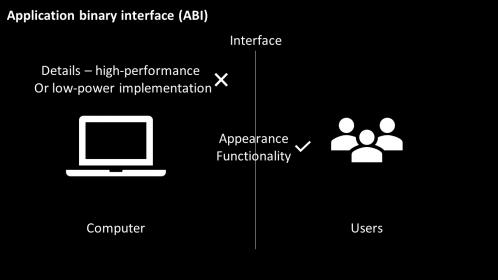

Application binary interface, get this right and RISC-V is all yours

Starting a career in static timing analysis domain, and now actively working on an opensource implementation flow of RISC-V architecture, has been a journey. For last couple of months, I guess from around March this year, I was hooked to RISC-V buzz which was all over my Linkedin, my messages.

Being an STA and Physical design engineer,… Read More

ARM tests out TSMC 10FinFET – with two cores

About 13 months ago, the leak blogs posted news of “Artemis” on an alleged ARM roadmap slide, supposedly a new 16FF ARM core positioned as the presumptive successor to the Cortex-A57. Now, we’re finding out what “Artemis” may actually be, inside a multi-core PPA test chip on TSMC 10FinFET.… Read More

Reducing Dynamic and Static Power in Memories

Sequential approaches to power reduction work well on logic implemented using standard cells. But part of every SoC, sometimes a very large part, is taken up with embedded memories for which alternative approaches are required. Not only do these memories occupy up to half of the area they also account for as much as 75% of the power… Read More