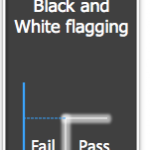

Last week GLOBALFOUNDRIES and Mentor Graphics presented at the Tech Design Forum on how they collaborated on a third generation DFM flow. When I reviewed the slides of the presentation it really struck me on how the old thinking in DRC (Design Rule Checking) of Pass/Fail for layout rules had been replaced with a score represented… Read More

Tag: drc

Third Generation DFM Flow: GLOBALFOUNDRIES and Mentor Graphics

Introduction

Mentor Graphics and GLOBALFOUNDRIES have been working together for several generations since the 65nm node on making IC designs yield higher. Michael Buehler-Garcia, director of Calibre Design SolutionsMarketing at Mentor Graphics spoke with me by phone today to explain how they are working with GLOBALFOUNDRIES… Read More

Aug 25th in Fremont, CA – Hands on Calibre workshop: DRC, LVS, xRC, ERC, DFM

I’ve blogged about the Calibre family of IC design tools before:

Smart Fill replaced Dummy Fill Approach in a DFM Flow

DRC Wiki

Graphical DRC vs Text-based DRC

Getting Real time Calibre DRC Results with Custom IC Editing

Transistor-level Electrical Rule Checking

Who Needs a 3D Field Solver for IC Design?

Prevention is Better… Read More

August 11th – Hands-on Workshop with Calibre: DRC, LVS, DFM, xRC, ERC

I’ve blogged about the Calibre family of IC design tools before:

Smart Fill replaced Dummy Fill Approach in a DFM Flow

DRC Wiki

Graphical DRC vs Text-based DRC

Getting Real time Calibre DRC Results with Custom IC Editing

Transistor-level Electrical Rule Checking

Who Needs a 3D Field Solver for IC Design?

Prevention is Better… Read More

A Birds-Eye Overview of DRC+

The GlobalFoundries DRC+ platform is one of the most innovative DFM technologies and was well represented at #48DAC. In case you missed it, here is a reprint of a DRC+ overview from GFI just prior to #48DAC:

DRC (Design Rule Constraints) are the fundamental principles in constraining VLSI (Very Large Scale Integration) circuit… Read More

GLOBALFOUNDRIES 28nm Design Ecosystem!

GLOBALFOUNDRIES will show off its 28nm design ecosystem at #48DAC next week in San Diego. The company will feature a full design ecosystem for its 28nm High-k Metal Gate (HKMG) technology, including silicon-validated flows, process design kits (PDKs), design-for-manufacturing (DFM), and intellectual property (IP) in partnership… Read More

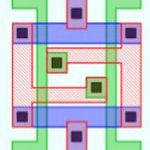

Graphical DRC vs Text-based DRC

Introduction

IC designs go through a layout process and then a verification of that layout to determine if the layout layer width and spacing rules conform to a set of manufacturing design rules. Adhering to the layout rules will ensure that your chip has acceptable yields.

At the 28nm node a typical DRC (Design Rule Check) deck will… Read More

DRC/DFM inside of Place and Route

Intro

Earlier this month I drove to Mentor Graphics in Wilsonville, Oregon and spoke with Michael Buehler-Garcia, Director of Marketing and Nancy Nguyen, TME, both part of the Calibre Design to Silicon Division. I’m a big fan of correct-by-construction thinking in EDA tools and what they had to say immediately caught my… Read More

New ERC Tools Catch Design Errors

A growing number of reports highlight a class of design errors that is difficult to check using more traditional methods, and can potentially affect a wide range of IC designs, especially where high reliability is a must.By Matthew Hogan

Today’s IC designs are complex. They contain vast arrays of features and functionality in … Read More

So, Why Not Just Write Better Rules?

In my submission about TSMC making some DFM analysis steps mandatory at 45nm (see “TSMC’s DFM Announcement”), I ended with a question about why the foundries can’t just write better design rules (and rule decks) to make sure all designs yield well. Here’s my take on this complicated question.… Read More