In modern electronic industry PCBs are required to accommodate highly dense circuits with large number of components and complex routing spaces. While the complexity is increasing, the time-to-market is decreasing. In such a scenario, there is no other option than to reduce the design time by employing innovative editing options… Read More

Tag: drc

Experts Talk at Mentor Booth

It’s less than four weeks to go at DAC 2015 and the program is final now. So I started investigating new technologies, trends, methodologies, and tools that will be unveiled and discussed in this DAC. In the hindsight of the semiconductor industry over the last year, I see 14nm technologies in the realization stage and 10nm beckoning… Read More

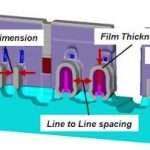

Chips Are Going 3D, DRC Needs to Go 3D Too

The last paradigm shift in DRC was around 0.35um when designs got too large to handle as flat data, and hierarchical approaches were required. Back then the design rules themselves were not that complex, the explosion of data volume came from the complexity of the design itself. But each process node added more design rules intricacies… Read More

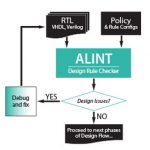

Design Rule Checking (DRC) Meets New Challenges

The traditional batch-oriented DRC process run as a final check to ensure compliance with foundry yield goals is quickly moving toward a concurrent DRC process performed early and often throughout design, especially at the 28 nm and smaller process nodes. What are the technology factors causing this change?

- Increasing number

Using Cadence PVS for Signoff at TowerJazz

TowerJazzis a specialty foundry that provides IC manufacturing into several markets, like: RF, high-performance analog, power, imaging, consumer, automotive, medical, industrial and aerospace/defense. In June there was a presentation from Ofer Tamir of TowerJazz at DACin the Cadence theatre, so I had a chance this week … Read More

Aldec Can Ensure Smooth System Integration

Tools, tools, tools. Designs are rapidly changing, JESD204b, Hybrid Memory cube and all other Gigabit serialization schemes are here to stay. RIP DDR. This means board level simulations with respect to firmware (FPGA) are going to be more challenging than ever. Why? you ask, especially if the board layout is simpler? True, but… Read More

FinFET & Multi-patterning Need Special P&R Handling

I think by now a lot has been said about the necessity of multi-patterning at advanced technology nodes with extremely low feature size such as 20nm, because lithography using 193nm wavelength of light makes printing and manufacturing of semiconductor design very difficult. The multi-patterning is a novel semiconductor manufacturing… Read More

Show Me How To Get Better DRC and LVS Results For My SoC Design

Most IC engineers learn best by hands-on experience when another more experienced person can show us what to do. If you cannot find that experienced person, then the next best thing is a video from an expert. I was surprised to find out that video was so important today that the #2 most viewed web site on the Internet was www.youtube.com… Read More

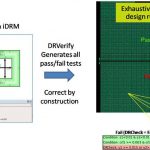

Verifying DRC Decks and Design Rule Specifications

DRVerify is part of the iDRM design rule compiler platform from Sage DA, something that I have been personally involved with for the past three years. DRVerify is mainly used to verify third party design rule check (DRC) decks and ensure that they correctly, completely and accurately represent the design rule specification. In… Read More

An easier way to deal with design rule waivers (video)

At advanced nodes, design rules are necessarily more complex and restrictive. Although most of the time you can find a way to live with them, sometimes it’s necessary to seek a waiver from the foundry for a particular design feature. This involves documenting the feature, the design rules in question and the conditions under which… Read More