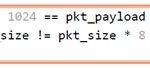

For the latest incremental improvements to its Riviera-PRO functional verification platform, Aldec has turned to streamlining random constraint performance. The new Riviera-PRO 2016.02 release also is now fully supported on Windows 10 and adds a new debugger tool.… Read More

Tag: debugging

A Brief History of FPGA Prototyping

Verifying chip designs has always suffered from a two-pronged problem. The first problem is that actually building silicon is too expensive and too slow to use as a verification tool (when it happens, it is not a good thing and is called a “re-spin”). The second problem is that simulation is, and has always been, too slow.

When Xilinx… Read More

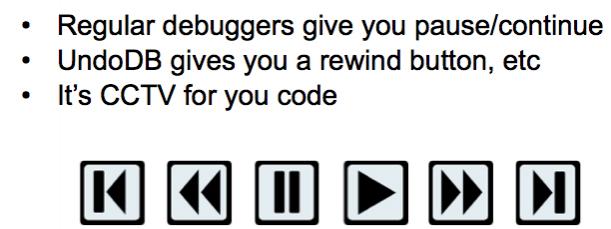

Cadence and Reverse Debugging

I wrote back in March about Undo Software. They have a reverse debugging solution called UndoDB (the DB is for debug, not database). I have a soft spot for reverse debugging ever since seeing one of the engineers at Virtutech type reverse single step and seeing the code back up a single instruction and realizing that literally months… Read More

Undo Your Code

When I was a Virtutech a few years ago we had a product called Hindsight. It looked close to magic when you used it since it allowed you to run code backwards. I assume that the technology is still lurking under the hood in Wind River’s Simics product, now part of Intel. The way the code worked is that as the software executed, Simics… Read More

Mark your Date for Semiconductor Design Vision

A very popular acronym is ‘WYSIWYG’ – What You See Is What You Get! This is very true and is important to visualize things to make it better in various aspects such as aesthetics, compactness, organization, structure, understandable for correction and so on; the most important, in case of semiconductor design, is being able to identify… Read More

What Makes A Designer’s Day? A Bottleneck Solved!

In an environment of SoCs with tough targets of multiple functionalities, smallest size, lowest power and fastest performance to achieve within a limited design cycle window in order to meet the rigid time-to-market requirements, any day spent without success becomes very frustrating for a designer. Especially during tape-out… Read More

Webinar: Parasitic Debugging made easy!

We cordially invite you to attend this webinar and learn how to quickly debug post layout designs. Concept Engineering is a privately held company based in Freiburg, Germany. It was, founded in 1990 to develop and market innovative schematic generation and viewing technology for use with logic synthesis, verification, test … Read More

Because X doesn’t always mark the exact spot

Digital hardware has a habit of deciding – based on the bias and behavior of transistors – to drive outputs to a 0, or a 1, or if commanded a high-impedance Z state. SystemVerilog recognizes a fourth state: X, the “unknown” state a simulator has trouble inferring.

Simulators have a choice. Under X-optimism, they can convert the unknown… Read More

Debugging Complex Embedded System – How Easy?

In today’s world of semiconductor design with SoCs having complex IPs, hardware and software working together on a single chip, it’s hard to imagine a system without embedded software into it. But it is easy to guess how difficult it would be to test that hardware and software embedded system. And often there is limited window of … Read More

Beyond one FPGA comfort zone

Unless you are a small company with one design team, the chance you have standardized on one FPGA vendor for all your needs, forever and ever, is unlikely. No doubt you probably have a favorite, because of the specific class of part you use most often or the tool you are most familiar with, but I’d bet you use more than one FPGA vendor routinely.… Read More