In the semiconductor industry High-Level Synthesis (HLS) and SystemC have become essential tools, allowing engineers to model complex hardware designs using familiar C/C++ constructs. Yet, despite the widespread adoption of these languages, the debugging workflows in hardware development lag far behind those in software… Read More

Tag: debugging

CEO Interview with David Zhi LuoZhang of Bronco AI

David Zhi LuoZhang is Co-Founder and CEO of Bronco AI with extensive experience in building AI systems for mission-critical high-stakes applications. Previously while at Shield AI, he helped train AI pilots that could beat top human F-15 and F-16 fighter pilots in aerial combat. There, he created techniques to improve ML interpretability… Read More

Formal-based RISC-V processor verification gets deeper than simulation

The flexibility of RISC-V processor IP allows much freedom to meet specific requirements – but it also opens the potential for many bugs created during the design process. Advanced processor features are especially prone to errors, increasing the difficulty and time needed for thorough verification. Born out of necessity, … Read More

Visual Debug for Formal Verification

Success with Open-Source Formal Verification

The dream of 100% confidence is compelling for silicon engineers. We all want that big red button to push that magically finds all of our bugs for us. Verification, after all, accounts for roughly two-thirds of logic design effort. Without that button, we have to create reference models,… Read More

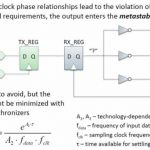

Up front phases improve CDC analysis

Many tools find clock domain crossings (CDCs) in FPGA designs. Some don’t find the right ones since they don’t comprehend things like in-house synchronizer constructs. Some find too many based on misunderstanding intent, inaccurate constraints, and other factors that lead to noise.… Read More

More on HAPS hybrid prototyping for ARMv8 with Linaro

A few weeks ago we previewed a Synopsys webinar describing how they are linking the ARM Juno Development Platform with the HAPS-80 and HAPS ProtoCompiler environment. I’ve had a look at the archived event and have some additional thoughts.… Read More

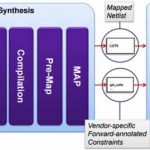

One FPGA synthesis flow for different IP types

Both Altera and Xilinx are innovative companies with robust ecosystems, right? It would be a terrible shame if you located the perfect FPGA IP block for a design, but couldn’t use it because it was in the “wrong” format for your preferred FPGA. What if there were a way around that?

There is a compelling argument to use each FPGA vendor’s… Read More

Debugging is the whole point of prototyping

The prototype is obviously the end goal of FPGA-based prototyping, however success of the journey relies on how quickly defects can be found and rectified. Winning in the debug phase involves a combination of methodology, capability, and planning. Synopsys recently aired a webinar on their HAPS environment and its debug ecosystem.… Read More