It requires lateral thinking in bringing new innovation into conventional solutions to age-old hard problems. While the core logic design has evolved adding multiple functionalities onto a chip, now called SoC, the structural composition of DFT (Design for Testability) has remained more or less same based on XOR-based compression… Read More

Tag: coverage

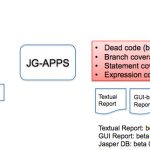

A Robust Lint Methodology Ensures Faster Design Closure

With the increase in SoC designs’ sizes and complexities, the verification continuum has grown larger to an extent that the strategies for design convergence need to be applied from the very beginning of the design flow. Often designers are stuck with never ending iterations between RTL, gate and transistor levels at different… Read More

How many coats cover this SoC?

“Most interior paint covers with one coat.” Back when there was something called a newspaper, this was an actual blurb in the home improvement pages, section 3, part 8, page 5 of the Chicago Tribune on Sunday, August 13, 1961. Even then, marketers were catering to consumers looking to cut corners and save time, and one-coat coverage… Read More

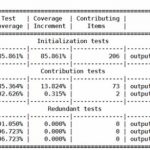

Verification plans overcome hope-based coverage

Coverage is an important yet elusive metric for design verification. It often seems 90% of coverage comes with 10% of the effort, and getting the final 10% covered takes the remaining 90% of a project. Usually, it takes another tool or methodology to get at the 10% the first tool missed. With 100% closure difficult, most teams inspect… Read More

Improve Test Robustness & Coverage Early in Design

In a semiconductor design, keeping the design testable with high test coverage has always been a requirement. However with shrinking technology nodes and large, dense SoC designs and complex logic structures, while it has become mandatory to reach close to 100% test coverage, it’s extremely difficult to cope with the explosion… Read More

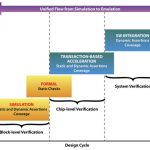

Assertions verifying blocks to systems at Broadcom

Speaking from experience, it is very difficult to get an OEM customer to talk about how they actually use standards and vendor products. A new white paper co-authored by Broadcom lends insight into how a variety of technologies combine in a flow from IP block simulation verification with assertions to complete SoC emulation with… Read More

Formal Going Mainstream

In Mike Muller’s keynote at DAC he wanted to make formal approaches an integral part of writing RTL. After all, formal captures design intent and then, at least much of the time, can verify whether the RTL written actually matches that intent. Today, formal is not used that way and is typically something served “on the side” by specialist… Read More