Register Transfer Level (RTL) is a crucial and valuable concept in digital hardware design. Over the years, it has played a fundamental role in enabling design of complex digital chips. By abstracting away implementation details and providing a clear description of digital behavior, RTL has contributed significantly to the… Read More

Tag: congestion

Webinar: Optimizing QoR for FPGA Design

You might wonder why, in FPGA design, you would go beyond simply using the design tools provided by the FPGA vendor (e.g. Xilinx, Intel/Altera and Microsemi). After all, they know their hardware platform better than anyone else, and they’re pretty good at design software too. But there’s one thing none of these providers want to… Read More

Making a smart city like Austin smarter

One of the takeaways from the recent #NXPFTF in Austin was the potential for smart cities. As the EDA industry gathers again for @53rdDAC, visitors will see firsthand how much high-tech talent there is in #ATX – and how big a challenge is developing.… Read More

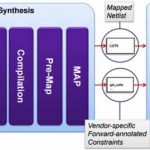

One FPGA synthesis flow for different IP types

Both Altera and Xilinx are innovative companies with robust ecosystems, right? It would be a terrible shame if you located the perfect FPGA IP block for a design, but couldn’t use it because it was in the “wrong” format for your preferred FPGA. What if there were a way around that?

There is a compelling argument to use each FPGA vendor’s… Read More

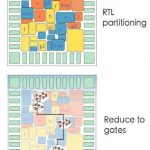

Decisive Floorplanning for Faster Design Closure

Semiconductor design automation at system level is gaining its due importance today. It needs an effective, efficient, and seamless flow from system up to silicon. There is lot of effort going on for automating SoC design exploration at system level but that eventually stops at RTL; another level of flow automation takes over … Read More

A Complete Scalable Solution for IP Signoff

In an SoC world driven by IP, where an SoC can have hundreds of IP (sourced not only from 3[SUP]rd[/SUP] party but also from internal business units which can have a lot of legacy) integrated together, it has become essential to have a comprehensive and standard method to verify and signoff the IP. Additionally, these checks must … Read More

Untangling snags earlier and reducing area by 10%

The over 20 years of experience behind Synopsys Design Compiler is getting a new look for 2014, and we had a few minutes with Priti Vijayvargiya, director of product marketing for RTL synthesis, to explore what’s in the latest version of the synthesis tool.

Previewed today, Synopsys Design Compiler 2013.12 continues to target … Read More

Start With The End In Mind – For Complete & Fast Success!

There is always a rush to converge a semiconductor design toward faster closure, amid increasing divergent trends of multiple IPs and high complexities of various functionalities on a single chip. Every design house struggles hard to evolve its customized design flows with several short paths patched up to fix issues, global… Read More

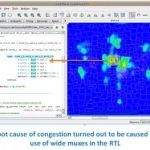

How to reduce routing congestion in large Application Processor SoC?

Application Processor SoC integrates more and more functions, generation after generation, challenging performance, cost, power efficiency, reliability, and time-to-market. But the maximum die size can’t increase, at least because of the constraints linked with wafer production, manufacturability, yield and finally… Read More

SoC Implementation, Sometimes You Need a Plan B

I read two blogs this week that got me to thinking about contingencies in SoC implementation. By contingency I mean using an EDA tool flow from the leading vendor for logic synthesis and then discovering that you cannot route the design without expanding the die size after a few weeks of concerted effort, then having to come up with… Read More