SoC projects are running behind schedule as design and verification complexity has increased dramatically, so just adding more engineers, more tests and more compute aren’t the answer. The time is ripe to consider smarter ways to improve verification efficiency. The added complexity of multiple embedded processors, multiple… Read More

Tag: closure

Latest Pinpoint Release Tackles DRC and Trend Lines

After reading previous SemiWiki coverage on Dassault Systèmes and their ENOVIA Pinpoint solution, one big item seemed missing: how does this thing actually work? With all due respect to our other bloggers who covered when Dassault Systèmes acquired Pinpoint from Tuscany Design Automation, why Qualcomm is using Pinpoint, and… Read More

Verification plans overcome hope-based coverage

Coverage is an important yet elusive metric for design verification. It often seems 90% of coverage comes with 10% of the effort, and getting the final 10% covered takes the remaining 90% of a project. Usually, it takes another tool or methodology to get at the 10% the first tool missed. With 100% closure difficult, most teams inspect… Read More

Automating PCB Timing Closure, Saving Up to 67%

The benefits of using EDA software is that it can automate a manual process, like PCB timing closure, saving you both time and engineering effort. This point was demonstrated today as Cadenceadded new timing-closure automation to their Allegroproduct family, calling it Allegro TimingVision. On Tuesday I spoke with Hemant Shah… Read More

Speeding Design Closure at DAC

At DAC you can measure buzz by how many people are crowded into your booth. I saw a crowd at the Oasys booth, so stopped to take in their 10 minute overview presentation. Here’s what I learned.… Read More

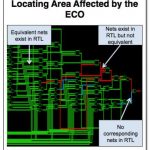

Formality Ultra, Streamline Your ECOs

One of the most challenging stages in an SoC design is achieving timing closure. Actually design closure is perhaps a better term since everything needs to come together such as clock tree, power nets, power budget and so on. Changes made to the design are known as ECOs (which stands for engineering change orders, a term that comes… Read More

CEO Interview: Jason Xing of ICScape Inc.

I recently had the opportunity to interview Jason Xing, Ph.D., CEO and President of ICScape, Inc. Below is a subset of the nearly two hour long interview.

How did you first become involved in EDA?

My EDA career started in the mid-90s when I started working on my PhD thesis at the University of Illinois in Urbana-Champaign. My thesis… Read More

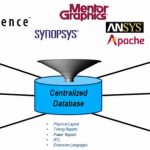

The Biggest EDA Company You’ve Never Heard Of

There’s this EDA company. They have over 100 tapeouts. They have a $28M in funding. They have 250 people. And you’ve never heard of them. Or at least I hadn’t.

They are ICScape. They started in 2005 with an investment from Acorn Campus Ventures and delivered their first product, ClockExplorer, in 2007 and their… Read More