Clock jitter rarely fails in obvious ways. In advanced-node designs, its impact is often indirect, emerging through subtle timing uncertainty, interaction with power delivery noise, and compounding effects across large clock networks. These behaviors can quietly erode margin and predictability, even when conventional… Read More

Tag: clock jitter

Infinisim Enables a Path to Greater Profitability and a Competitive Edge

Improved profitability and competitiveness are at the very heart of every enterprise. Achievements like this are usually attributed to corporate culture. Sometimes, it’s just being in the right place at the right time. Some organizations make huge investments with top-tier consulting companies to help find their way.

Recently… Read More

Silicon Creations Presents Architectures and IP for SoC Clocking

Design & Reuse recently held its IP-SoC Days event at the Hyatt Regency in Santa Clara. Advanced IP is now the fuel for a great deal of innovation in semiconductor design. This popular event allows IP providers to highlight the latest products and services and share a vision of the future. IP consumers can easily get updates on… Read More

Video EP2: A Detailed Look at the Most Effective Way to Conquer Clock Jitter with Samia Rashid

In this episode of the Semiconductor Insiders video series, Dan is joined by Samia Rashid, co-founder and president of Infinisim. Samia provides detailed background on clock jitter – what it is, what causes it and the various methods to address the problem. Samia describes the unique clock analysis technology developed… Read More

2025 Outlook with Samia Rashid of Infinisim

Tell us a little bit about yourself and your company.

I am Samia Rashid, co-founder and president of Infinisim. My background is quite diverse, spanning product management, manufacturing, sales, and mergers and acquisitions. Before founding Infinisim, I was with iManage, Inc., where I played a pivotal role in growing the company… Read More

A Closer Look at Conquering Clock Jitter with Infinisim

As voltages go down and frequencies increase, the challenges in chip design become increasingly complex and unforgiving. Issues that once seemed manageable now escalate, while new obstacles emerge, demanding our attention. Among these challenges, clock jitter stands out as a formidable threat. At its core, clock jitter is… Read More

Analyzing Clocks at 7nm and Smaller Nodes

In the good old days the clock signal looked like a square wave , and had a voltage swing of 5 volts, however with 7nm technology the clock signals can now look more like a sawtooth signal and may not actually reach the full Vdd value of 0.65V inside the core of a chip. I’ll cover some of the semiconductor market trends, and then challenges… Read More

Methodology to Minimize the Impact of Duty Cycle Distortion in Clock Distribution Networks

Synchronous circuits dominate the electronic world because clocking eases the design of circuits compared to asynchronous circuits. At the same time, clocking also introduces its share of challenges to overcome. No wonder, a tremendous amount of time and effort have been spent over the years on developing and implementing … Read More

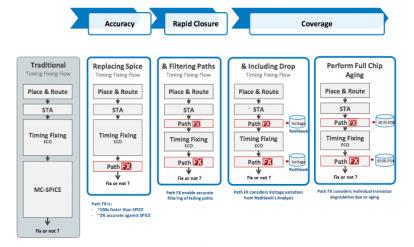

Have STA and SPICE Run Out of Steam for Clock Analysis?

At advanced nodes such as 7 and 5nm, timing closure and sign off are becoming much more difficult than before at 16nm. One area of chips that has increased in complexity dramatically and who’s correct operation is essential for silicon success is the clock tree. If the clock tree has excessive jitter, it will throw off every timing… Read More

Peering Over the Timing Edge

I wrote recently about a yield problem which mobile vendors have been finding for devices built in advanced technologies. This was a performance issue (the devices worked fine at lower clock speeds), pointing to a discrepancy in some devices between predicted and observed timing. These were experienced design teams, using state… Read More