We all know semiconductor design is getting harder. Much harder when you consider the demands of AI workloads and heterogeneous integration of many chiplets in a single package. This class of system demands co-optimization across the entire design flow. For example, functional verification, thermal analysis, signal and power… Read More

Tag: calibre 3dstack

3DIC Verification Methodologies for Advanced Semiconductor ICs

At the recent User2user conference, Amit Kumar, Principal Hardware Engineer, Microsoft, shared the company’s experience from building a 3DIC SoC and highlighted Siemens EDA tools that were used. The following is a synthesis of core aspects of that talk.

3DIC Challenges

Despite the numerous advantages of 3DIC technology, its… Read More

The Path to Chiplet Architecture

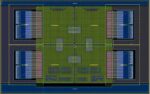

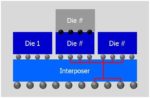

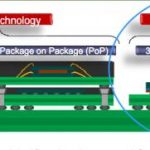

If you have anything to do with the semiconductor industry, you already know that one of the hottest areas for both manufacturing and EDA are systems designed with advanced packaging, basically putting more than one die (aka chiplets) in the same package.

When 3D packaging was first introduced, there were not really any effective… Read More

3DIC Physical Verification, Siemens EDA and TSMC

At SemiWiki we’ve written four times now about how TSMC is standardizing on a 3DIC physical flow with their approach called 3Dblox, so I watched a presentation from John Ferguson of Siemens EDA to see how their tool flow supports this with the Calibre tools. With a chiplet-based packaging flow there are new physical verification… Read More

Advances in Physical Verification and Thermal Modeling of 3DICs

If, like me, you’ve been paying too little attention to historically less glamorous areas of chip design like packaging, you’ll wake up one day and realize just how much things have changed and continue to advance and how interesting it’s become.

One of the main drivers here is the increasing use of chiplets to counter the decreasing… Read More

Physical Verification of 3D-IC Designs using TSVs

3D-IC design has become a popular discussion topic in the past few years because of the integration benefits and potential cost savings, so I wanted to learn more about how the DRC and LVS flows were being adapted. My first stop was the Global Semiconductor Alliance web site where I found a presentation about how DRC and LVS flows were… Read More