The World Affairs Council event, The Internet of Things: Global Implications of Merging the Physical and Digital Worlds, was hosted by Cadence last week. One thing I can tell you is that Cadence sure does know how to throw a party! They had me at free food and beer but the topic was also of great interest since my next project will involve… Read More

Tag: cadence

Intel is Still Missing Mobile!

Paul McLellan was on assignment in Hong Kong last week so I attended the Linley Mobile Conference and was not surprised Intel did not present. During the networking sessions I asked more than a dozen people why and the answers were pretty focused on “Intel still does not play well with others” and “Intel’s current mobile offerings… Read More

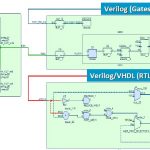

Ten Innovative Debugging Techniques – Pre & Post Layout

In a complex world of SoCs with multi-million gates and IPs from several heterogeneous sources, verification of a complete semiconductor design has become extremely difficult, and it’s not enough. In order to ascertain the right intent of the design throughout the design cycle, debugging at various stages of the design cycle… Read More

Cadence Acquires Jasper

Cadence announced today that it is acquiring Jasper Design Automation for $170M in an all-cash offer. Jasper has $24M in cash so it is really an acquisition for around $145M. i think that is around 4X revenue but I only know rumors about Jasper’s revenue numbers.

All the big 3 already have their own formal technology but the … Read More

Signoff Accurate Timing Analysis at Improved Run-time & Capacity

The semiconductor design sizes, these days, can easily be of the order of several hundred millions of cells, adding into the complexity of verification. Amid ever growing design sizes, it’s a must that the timing verification is done accurately. Normally Static Timing Analysis (STA) is done to check whether all clocks and signals… Read More

Does Processor IP still get the Lion’s share in 2013?

I think that the answer is pretty obvious, but the interesting point is to figure out which processor type, and which part of revenues, up-front license or royalties? One of my customers, let’s call him Mr. X, ask me to clarify this point. Mr. X has bought the excellent report from Gartner “Market Share: Semiconductor Design Intellectual… Read More

Addressing MCU Mixed Signal Design Challenges

The emerging market for IoT and wearable devices are designed with mixed-signal IP that includes: embedded CPU, flash, analogue and radio.EDA and IP companies have recently worked together to allow us to design an MCU with mixed-signal IP blocks more efficiently. This morning I attended a webinar with presenters from ARMand … Read More

IP Reuse and Management in Monterey!

One of the benefits of being part of SemiWiki is building relationships with a wide variety of companies covering every semiconductor design application imaginable. We are blessed, absolutely. Another benefit of being part of SemiWiki are the invitations to attend, participate, and even organize events such as EDPS. Last year… Read More

FinFET Custom Design

At CDNLive, Bob Mullen of TSMC gave a presentation on their new custom FinFET flow, doing design, and verifying designs. At 16nm there are all sorts of relatively new verification problems such as layout dependent effects (LDE) and voltage dependent design rules. We had some of this at 20nm but like most things in semiconductor,… Read More

Automating Analog Verification in Virtuoso

Digital designers have been automating the functional verification process for many years now, however when you talk to an analog designer about how they do verification you quickly realize that the typical process is quite ad-hoc and little automated. Necessity does create an opportunity so the software engineers at Methodics… Read More