When situation demands, multiple solutions appear with a slight lag of time. Similar is the story with estimating and optimizing power at SoC level. In the SoC era, power has become a critical criterion long ago, and there are tools available for power analysis and optimization. However, with more mobile and IoT (Internet of Things)… Read More

Tag: cadence

What Does Legal Sea Foods Have to Do With EDA?

When I drive down to Silicon Valley I usually listen to podcasts rather than just listen to the radio. One that I especially like is Russ Robert’s EconTalk, which has an hour-long episode every Monday morning on a wide range of different aspects of Economics. Normally he interviews an economist. He has also interviewed the… Read More

Cadence 2015 Q2 Results

Let’s start by getting the financial stuff out of the way. Revenue was $416 million; non-GAAP operating margin was 28%; non-GAAP EPS was $0.27; and operating cash flow was $122 million (up at lot, it was just $47M in Q1 and $69M in Q2 of 2014).

The thing that the financial types are most interested in are the changes to Cadence’s… Read More

How Emulation Enables Complex Power Intent Modeling

As the number of CPU, GPU, and IP is growing in an SoC, power management is becoming more and more a complex task in itself. A single tool or methodology may not be enough for complete power management and verification of an SoC. In an SoC, there can be multiple modes of operations involving hardware and software interactions, different… Read More

Which High B/W Memory to Select after DDR4?

Once upon a time, RAM technology was the driver of the semiconductor process. DRAM products were the first to be designed on a newest technology node and DRAM was used as a process driver. It was 30 years ago and the most aggressive process nodes were ranging between 1um and 1.5 um (1 500 nm!). Then in the 1990 the Synchronous Dynamic … Read More

Tackling Layout Gradient Effects in 16 nm FinFET using Layout Automation

My first exposure to automating IC layout was back in the 1980’s at Intel where I coded a layout compiler to auto-generate about 6% of a graphics processor chip. The need to use automation for IC layout continues today, and with the advent of FinFET technology there are some new challenges like layout gradient effects that … Read More

What’s New in Functional Verification Debug

We often think of EDA vendors competing with each other and using proprietary data formats to make it difficult for users to mix and match tools, or even create efficient flows of tools. At the recent DAC event in San Francisco I was pleasantly surprised to hear that two EDA vendors decided to cooperate instead of create incompatible… Read More

Eyes Meet Innovations at DAC

It gives me a very nice, somewhat nostalgic, feeling after attending the 52[SUP]nd[/SUP] DAC. There was a period during my final academic year in 1990 and my first job when I used to search through good technical papers in DAC proceedings and try implementing those concepts in my project work. In general, representation from ‘R&D… Read More

Next Generation Formal Technology to Boost Verification

With growing complexities and sizes of SoCs, verification has become a key challenge for design closure. There isn’t a single methodology that can provide complete verification closure for an SoC. Moreover creation of verification environment including hardware, software, testbench and testcases requires significant … Read More

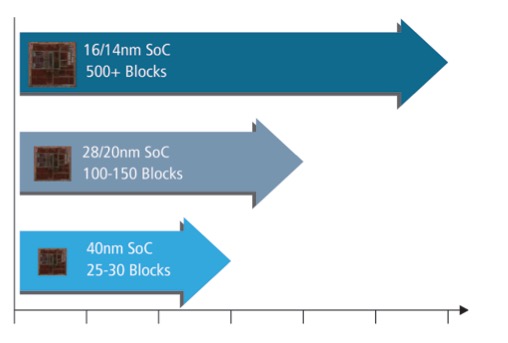

Logic Synthesis Reborn

Combine the pressures of Moore’s Law which enable billion transistor SoCs and the shortened time to market from consumer electronics product cycles and you have the perfect storm for EDA tool vendors. A modern SoC can have 500 or more blocks, creating both a design and verification challenge. How in the world do you write … Read More