Cadence has done a good job of keeping up with the needs of analog RF designs. Of course, the term RF used to be reserved for a thin slice of designs that were used specifically in RF applications. Now, it covers things like SerDes for networking chips that have to operate in the gigahertz range. Add that to the trend of combining RF and… Read More

Tag: cadence

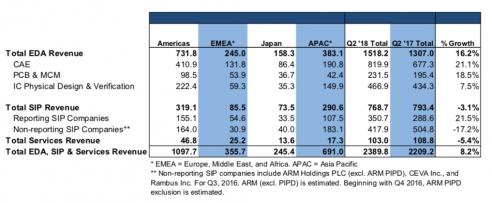

Who is Responsible for SIP Revenue Decline in Q2 2018?

According with ESDA, EDA revenues have grown YoY by 16.2% in Q2 2018, and this is the good news for our industry. The bad news is the decline of SIP (Design IP) revenues, by (3.1%) at the same time. As far as I am concerned, this figure looks weird, so I will try to understand the reason why SIP category can go wrong in a healthy EDA market,… Read More

EDA Cost and Pricing

This is the nineteenth in the series of “20 Questions with Wally Rhines”

When I moved from the semiconductor industry to Mentor, I expected most of my technology and business experience to apply similarly in EDA software. To some extent, that was correct. But there was a fundamental difference that required a change… Read More

AVANTI: The Acquisition Game

This is the eighteenth in the series of “20 Questions with Wally Rhines”

Gerry Hsu’s departure from Cadence to form Avanti (originally named ArcSys) is chronicled in legal testimony as accusations of theft of software were followed by legal battles, financial awards and even prison terms. Mentor and Synopsys were… Read More

Meeting Analog Reliability Challenges Across the Product Life Cycle

Create a panel discussion about analog IC design and reliability and my curiosity is instantly piqued, so I attended a luncheon discussion at #55DAC moderated by Steven Lewis of Cadence. The panelists were quite deep in their specialized fields:… Read More

A True Signoff for 7nm and Beyond

The Tale of Three Metrics

Meeting PPA (Performance, Power and Area) target is key to a successful design tapeout. These mainstream QoR (Quality of Results) metrics are rather empirical yet inter-correlated and have been expanded to be linked with other metrics such as yield, cost and reliability. While the recent CPU performance… Read More

Cadence Update on AMS Design and Verification at #55DAC

As a blogger in the EDA industry I get more invitations to meet with folks at DAC than I have time slots, so I have to be a bit selective in who I meet. When the folks at Cadence asked me to sit down and chat with Mladen Nizic I was intrigued because Mladen is so well-known in the AMS language area and he’s one of the authors of, The Mixed-Signal… Read More

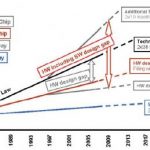

An update on the Design Productivity Gap

Over a decade ago, a group of semiconductor industry experts published a landmark paper as part of the periodic updates to the International Technology Roadmap for Semiconductors, or ITRS for short (link). The ITRS identified a critical design productivity gap. The circuit capacity afforded by the Moore’s Law pace of technology… Read More

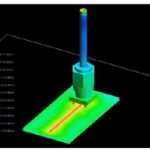

Accelerating the PCB Design-Analysis Optimization Loop

With the increasing complexity and diversity of the mechanical constraints and electrical requirements in electronic product development, printed circuit board designers are faced with a number of difficult challenges:

- generating accurate (S-parameter) simulation models for critical interface elements of the design

Verification Importance in Academia

“Testing can only prove the presence of bugs, not their absence,” stated the famous computer scientist Edsger Dijkstra. That notion rings true to the many college participants of the Hack@DAC competition offered during DAC 2018 in San Francisco. The goal of this competition is to develop tools and methods for identifying security… Read More