Mike Gianfagna, a fellow SemiWiki blogger and a one-time colleague at Atrenta shared a useful piece of marketing advice. If your company is not the biggest fish in the pond and you want to appear more significant, team up with other companies to put on an event, say a webinar. Pick your partners so that you can jointly offer a larger,… Read More

Tag: bernard murphy

Sensor Fusion in Hearables. A powerful complement

I must admit I’m impressed with how CEVA is pulling together foundational solutions for advanced consumer electronics. This through their own technologies (DSP, audio, vision, neural nets) and a rapid pace of partnerships, investments and acquisitions. Off the top of my head, I remember recent announcements on Immervision… Read More

Arm Design Reviews add Mentor for Verification Review

Arm and Mentor Recently announced that the Arm Design Reviews program now offers Mentor help in verification design reviews. I talked to Paul Williams (Sr Consultant and Verification Practice Lead at Mentor Graphics) and Peter Lewin (Dir. Mktg at Arm Partner Enablement Group) to get more insight into Arm Design Services, particularly… Read More

Cache Coherence Everywhere may be Easier Than you Think

I attended one of the Arm partner events in Cambridge many years ago, when they first talked about the coherent hub for managing cache coherence. I was impressed, but the obvious question even then was how any non-Arm IP was going to hook into this hub. They had a solution, of course, the ACE interface, and I left satisfied. As is the … Read More

CEO Interview: Andreas Kuehlmann of Tortuga Logic

You may remember Andreas from his time at Synopsys, where he led the new Software Integrity Business Unit. He joined Tortuga Logic a couple of months ago to lead the company. Given his background in software security, I was eager to get a CEO interview. Andreas is a EE with background at IBM in the PowerPC and EDA. He directed Cadence… Read More

Low Energy Intelligence at the Extreme Edge

Intelligence at the edge is a hot topic these days. Not having to go all the way to the cloud to recognize objects, faces, speech and so on. But I find promoters can be rather fuzzy about what they mean by “the edge”. For many, intelligence at the edge means intelligence closer to the edge than the cloud. In a gateway for example. Not actually… Read More

Israel and Automotive Safety. More Active Than You May Think.

CadenceLIVE ran a session recently in Europe which I thought would be interesting to check out, especially around automotive needs. The live sessions were too early/late for me (middle of the night) and sadly the talks I really wanted to hear weren’t recorded. Instead, I dug around for updates on automotive electronics in Europe.… Read More

Covering Configurable Systems. Innovation in Verification

Covering configurable systems is a challenge. What’s a good strategy to pick a small subset of settings and still get high confidence in coverage? Paul Cunningham (GM, Verification at Cadence), Jim Hogan and I continue our series on research ideas, here an idea from software testing which should also apply to hardware. Feel free… Read More

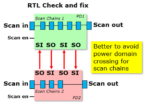

Power in Test at RTL Defacto Shows the Way

In the early days of Atrenta I met with Ralph Marlett, a distinguished test expert with many years of experience at Zuken and Recal Redac. He talked me into believing we could do meaningful static analysis for DFT-friendliness at RTL. His work with us really opened my eyes to the challenges that test groups face in integrating their… Read More

Randomization Fools Us Some of the Time

Though hopefully not some of us all of the time. Randomization is a technique used in verification to improve coverage in testing. You develop tests you know you have to run, then you throw randomization on top of that to search around those starter tests, to explore possibilities you haven’t considered. Truly random tests are not… Read More