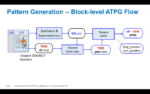

I first learned about ATPG – Automatic Test Program Generation in the 1980s at Silicon Compilers, then continued in the 90s at Viewlogic with the Sunrise tools, so it was illuminating to get an update from Synopsys on their ATPG technology by attending a webinar. Synopsys over the years has developed a family of test tools, shown … Read More

Tag: atpg

Webinar: Advances in ATPG: From Power and Timing Awareness to Intelligent Pattern Search with AI

Date: Jan 14, 2026 | 10:00 AM PST

Featured Speakers:

- Srikanth Venkat Raman, Product Management Director, Synopsys

- Khader Abdel-Hafez, Scientist, Synopsys

- Theo Toulas, R&D Principal Engineer, Synopsys

- Bruce Xue, Staff Engineer, Synopsys

As System-on-Chip (SoC) designs become increasingly complex, meeting test quality

Propelling DFT to New Levels of Coverage

Siemens recently released a white paper on a methodology to enhance test coverage for designs with tight DPPM requirements. I confess when I first skimmed the paper, I thought this was another spin on fault simulation for ASIL A-D qualification, but I was corrected and now agree that while there are some conceptual similarities… Read More

The First Automotive Design ASIC Platform

Alchip Technologies, Ltd. is a company that specializes in ASIC (Application-Specific Integrated Circuit) design and manufacturing. They are known for providing high-performance and customized ASIC solutions for a variety of applications. Alchip works with clients to design and develop integrated circuits that meet specific… Read More

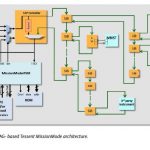

Tessent SSN Enables Significant Test Time Savings for SoC ATPG

SoC test challenges arise due to the complexity and diversity of the functional blocks integrated into the chip. As SoCs become more complex, it becomes increasingly difficult to access all of the functional blocks within the chip for testing. SoCs also can contain billions of transistors, making it extremely time-consuming… Read More

Getting Physical to Improve Test – White Paper

One of the most significant and oft repeated trends in EDA is the use of information from layout to help drive other parts of the design flow. This has happened with simulation and synthesis among other things. Of course, we think of test as a physical operation, but test pattern generation and sorting have been netlist based operations.… Read More

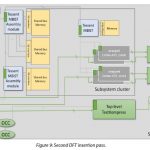

Bringing Hierarchy to DFT

Hierarchy is nearly universally used in the SoC design process to help manage complexity. Dealing with flat logical or physical designs proved unworkable decades ago. However, there were a few places in the flow where flat tools continued to be used. Mentor lead the pack in the years around 1999 in helping the industry move from … Read More

ITC shines light on new Mentor Test announcements

The 50th International Test Conference was just held in Washington DC, where papers, sessions, workshops and announcements addressing the increasing complexity and expanding use of semiconductors showed that innovations in test are crucial to design and product success. Test methodologies and even the scope of test have … Read More

Automotive Market Pushing Test Tool Capabilities

It’s easy to imagine that the main impetus for automotive electronics safety standards like ISO 26262 is the emergence of autonomous driving technology. However, even cars that do not offer this capability rely heavily on electronics for many critical systems. These include engine control, braking, crash sensors, and stability… Read More

Hierarchical RTL Based ATPG for an ARM A75 Based SOC

Two central concepts have led to the growth of our ability to manage and implement larger and larger designs: hierarchy and higher levels of abstraction. Without these two approaches the enormous designs we are seeing in SOCs would not be possible. Hierarchy in particular allows the reuse of component blocks, such as CPU cores.… Read More