In the semiconductor world we have divided our engineering talent up into many adjacent disciplines and each comes with their own job titles: Design engineers, Verification engineers, DFT engineers, Test engineers. When first silicon becomes available then everyone on the team, and especially management all have a few big … Read More

Tag: atpg

Test Compression for Mission Critical SoCs

With the advent of the Internet-of-Things (IoT), Industry 4.0, Cognitive Computing, and autonomous vehicles and robots we are seeing an unprecedented number of systems-on-a-chip (SoCs) going into mission-critical applications. To accomplish the complexity of these applications, SoCs are being manufactured in leading-edge… Read More

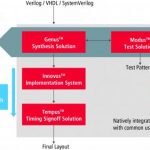

Automotive IC Design Requires a Unique EDA Tool Emphasis

Semiwiki readers are no doubt very familiar with the increasing impact of the automotive market on the semiconductor industry. The magnitude and complexity of the electronic systems that will be integrated into upcoming vehicle designs reflects the driver automation, safety, and entertainment features that are in growing… Read More

Finding Transistor-level Defects Inside of Standard Cells

In the earliest days of IC design the engineering work was always done at the transistor-level, and then over time the abstraction level moved upward to gate-level, cell-level, RTL level, IP reuse, and high-level modeling abstractions. The higher levels of abstraction have allowed systems to be integrated into an SoC that can… Read More

Reducing the Cost of SoC Testing

Every year certain technology themes appear, like at ITC this year a big theme was how to reduce the cost of SoC testing. I spoke with Rob Knoth of Cadence by phone to hear more about this cost of test theme. Rob gave me an example of an SoC that takes 27 seconds on a tester, so at $0.04 per second in test costs amounts to $1.08 per part. If you… Read More

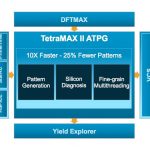

EDA Tool for ATPG – Refactor or Rewrite?

In the life of all EDA software tools comes that moment when new requirements make developers stop and ask, should I continue to refactor the existing code or just start all over from scratch using a new approach? Synopsys came to that junction point when ATPG run times were reaching days or even weeks on the largest IC designs, something… Read More

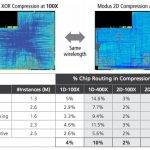

Cadence Adds New Dimension to SoC Test Solution

It requires lateral thinking in bringing new innovation into conventional solutions to age-old hard problems. While the core logic design has evolved adding multiple functionalities onto a chip, now called SoC, the structural composition of DFT (Design for Testability) has remained more or less same based on XOR-based compression… Read More

Three New Things from ITC this year

The NFL has its annual Super Bowl contest each year, EDA vendors attend DAC, then the test folks attend ITCwhich was in Anaheim a few weeks ago. I’ve marketed ATGP, BIST and DFT tools before so I like to keep updated on what’s happening at conferences like ITC. Robert Ruiz from Synopsys spoke with me by phone to provide … Read More

What’s Testing Design Limits at ITC?

The 46[SUP]th[/SUP] IEEE International Test Conference (ITC) will be held the week of October 5, 2015 at the Disneyland Hotel Conference Center in Anaheim, California. ITC is where you will discover the latest ideas and learn about practical applications of test technologies.

As you take in panels, tutorials, presentations,… Read More

Addressing Moore’s Law with the First Law of Real Estate: Location, location, location

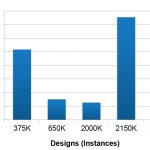

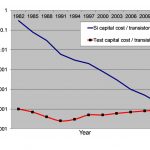

Design sizes and complexities have grown exponentially (it’s a Law!), and consequentially the task of silicon test has become proportionally more expensive. The cost of testing a device is proportional to the amount of test data that is applied, and therefore the time it takes, which in turn is proportional to both design size … Read More