You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

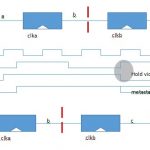

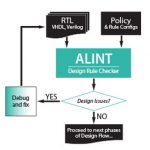

EDA verification tools generally do a great job of analyzing the written rules in digital design. Clock domain crossings (CDCs) are more like those unwritten rules in baseball; whether or not you have a problem remains indefinite until later, when retaliation can come swiftly out of nowhere.

Rarely as overt or dramatic as a bench-clearing… Read More

Multiple clock domains in FPGAs have simplified some aspects of designs, allowing effective partitioning of logic. As FPGA architectures get more flexible in how clock domains, regions, or networks are available, the probability of signals crossing clock domains has gone way up.… Read More

Tools, tools, tools. Designs are rapidly changing, JESD204b, Hybrid Memory cube and all other Gigabit serialization schemes are here to stay. RIP DDR. This means board level simulations with respect to firmware (FPGA) are going to be more challenging than ever. Why? you ask, especially if the board layout is simpler? True, but… Read More

I will say that as popular as DO-254 and the like is, I am not the fella for that. It can take the simplest of designs into a realm of test and verification like you have never seen before. Yes, when I am flying I happen to be a big fan of this rigorous testing but you will not find me doing that job anytime soon. While the topic is very dry, it … Read More

The difficulty of an engineering problem can be gauged by two things:

1) The number of attempts to generate a solution.

2) The degree of hyperbole used to describe the effectiveness of the latest solution.

The problem many folks in the EDA industry are after right now is clock domain crossings (CDCs) and the resulting metastability… Read More