You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

At 3nm and below, clock networks have quietly become the dominant limiter of SoC power, performance, and yield. Yet most advanced-node designs still rely on abstraction-based signoff methodologies developed when voltage headroom was generous and interconnect effects were secondary.

That assumption no longer holds

As supply… Read More

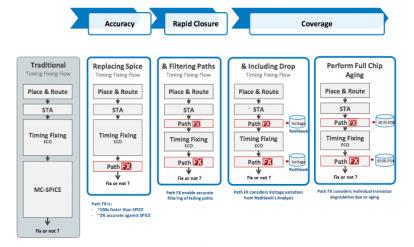

Static Timing Analysis (STA) has been an EDA tool category for many years now, yet with each new generation of smaller foundry process nodes come new physical effects that impact timing, requiring new analysis features to be added. For advanced process nodes, there are five different types of analysis that must be included when… Read More

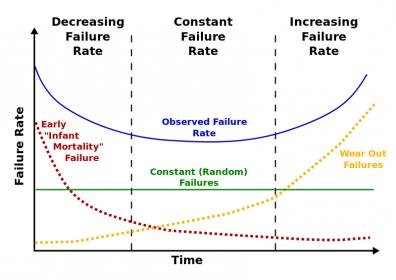

Semiconductor chips are all tested prior to shipment in order to weed out early failures, however there are some more subtle reliability effects that only appear in the longer term, like clock aging. There’s even a classic chart that shows the “bathtub curve” of failure rates over time:

If reality and expectations… Read More

We all know that designers work hard to reach design closure on SOC designs. However, what gets less attention from consumers is the effort that goes into ensuring that these chips will be fully operational and meeting timing specs over their projected lifetime. Of course, this is less important for chips used in devices with projected… Read More

I wrote recently about a yield problem which mobile vendors have been finding for devices built in advanced technologies. This was a performance issue (the devices worked fine at lower clock speeds), pointing to a discrepancy in some devices between predicted and observed timing. These were experienced design teams, using state… Read More

In case you missed the TSMC event, ANSYS and TSMC are going to reprise a very important topic – signing-off reliability for ADAS and semi-autonomous /autonomous systems. This topic hasn’t had a lot of media attention amid the glamor and glitz of what might be possible in driverless cars. But it now seems like the cold light of real … Read More

I was driving recently on highway 87 (San Jose) and wanted to merge left. I checked my side-mirror, checked the blind-spot detector, saw no problems and started to move over – and quickly swerved back when a car shot by on my left. What went wrong? My blind-spot detection, a primary feature in ADAS (advanced driver assistance systems,… Read More

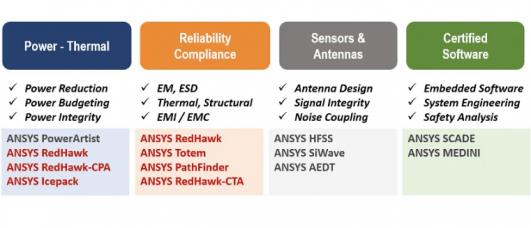

Ansys recently hosted a webinar on reliability signoff for FinFET-based designs, spanning thermal, EM, ESD, EMC and aging effects. I doubt you’re going to easily find a more comprehensive coverage of reliability impact and analysis solutions. If you care about reliability in FinFET designs, you might want to check out this webinar.… Read More