Alchip Technologies, a global leader in high-performance computing (HPC) and AI infrastructure ASICs, has officially launched its 2nm Design Platform, marking a major advancement in custom silicon design. The company has already received its first 2nm wafers and is collaborating with customers on the development of high-performance ASICs built on this next-generation node. This milestone positions Alchip among the earliest adopters of TSMC’s leading-edge technologies, with a clear roadmap that extends to both TSMC’s N2 (2nm) and upcoming A16 (1.6nm) process technologies.

Advanced Chiplets and Packaging for 2nm Compute Systems

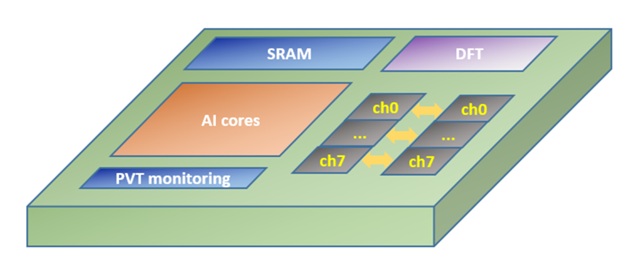

The new design platform delivers a full-stack methodology for building compute-dense, power-efficient ASICs on TSMC’s N2 node. It supports a broad set of chiplet integration strategies, enabling 2nm compute dies to work in tandem with 3nm or 5nm I/O chiplets. This approach supports a heterogeneous architecture that optimizes performance, yield, and design flexibility—critical in the post-Moore’s Law era.

Alchip’s platform also supports TSMC’s CoWoS®-S/R/L 2.5D/3D packaging, System on Integrated Chip (SoIC®-X) bonding, and is on track to support System on Wafer (SoW™) packaging for 3DICs. Additionally, die-to-die (D2D) IP and IO chiplet development are built into the platform, ensuring robust interconnect and thermal-aware design.

Overcoming N2 Design Complexity

TSMC’s N2 process represents its first gate-all-around (GAAFET) node, replacing FinFETs with nanosheet transistors. This shift offers notable benefits in performance, power efficiency, and area (PPA), with up to 10–15% speed gain or 25–30% power reduction over N3E. However, it also introduces significant layout and manufacturing challenges. These include tighter design rules, more complex power and signal routing, and new constraints around nanosheet stacking and variability.

Alchip’s 2nm Design Platform is engineered to address these issues head-on. The design flow is optimized to manage the increased diversity of standard cells and the denser transistor layouts introduced at N2. By anticipating placement, routing, and power integrity challenges early in the design process—before floorplanning or clock tree synthesis—Alchip reduces turnaround time while enhancing design predictability.

Power and Thermal Density Solutions

At 2nm, power and thermal density per square millimeter rise significantly due to increased gate counts and faster switching. Alchip’s methodology addresses this with thermal-aware floorplanning, advanced packaging co-optimization, and strategic power distribution planning. Even in the absence of native 2nm I/O chiplets, the platform supports mixed-node integration using 3nm and 5nm I/O for early deployment and yield optimization.

First-Pass Success, SoIC Demonstration, and A16 Transition

Alchip’s 2nm test chip achieved first-pass silicon success, validating both its methodology and IP stack. The design featured the company’s proprietary AP-Link-3D I/O interface, demonstrating full compatibility with SoIC-X chiplet interconnect. These results reinforce Alchip’s leadership in 3D integration and position it well for TSMC’s future process nodes, including A16™, which introduces backside power delivery and further transistor performance improvements.

Positioning for the TSMC N2 Era

TSMC began risk production on N2 in late 2024, with volume ramp expected in the second half of 2025. N2 introduces nanosheet GAAFETs, enabling better electrostatic control and design flexibility with variable channel widths. Alchip’s 2nm platform ensures customers are equipped to tap into these benefits while mitigating the risks associated with early-node development.

“We’re open for business and ready to support customers’ 2nm demand,” said Erez Shaizaf, CTO of Alchip Technologies. “Our new platform positions us as an industry leader, not only at 2nm but as we prepare for TSMC’s A16 era.”

“The is really just another milestone on our 2nm roadmap. Alchip’s 2nm platform is ready to work with key IP vendors, and we’ve been actively engaged with a couple of different companies on their 2nm ASIC developments. We anticipate this to be a very popular node for high-performance computing innovation,” explains Dave Hwang, General Manager, North America Business Unit.

About Alchip

Founded in 2003 and headquartered in Taipei, Alchip Technologies Ltd. is a leading global ASIC provider, specializing in HPC and AI applications. Its services span ASIC design, chiplet integration, 2.5D/3D packaging, and manufacturing management. Alchip serves top-tier system companies worldwide and is listed on the Taiwan Stock Exchange .

Also Read:

Alchip’s Technology and Global Talent Strategy Deliver Record Growth

Outlook 2025 with David Hwang of Alchip

Alchip is Paving the Way to Future 3D Design Innovation

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.