The success of our semiconductor eco-system depends on collaboration, so the annual TSMC OIP Event just held on September 30 at the San Jose Convention Center was a prime example of that. I didn’t attend this year, but I did follow up with Amit Nandaof Silvaco this week to hear about what they presented. As a consultant I’ve worked with Amit before when he was at Barcelona Design Inc., an interesting analog-compiler company, now part of Synopsys.

Related: EDA Mergers and Acquisitions Wiki

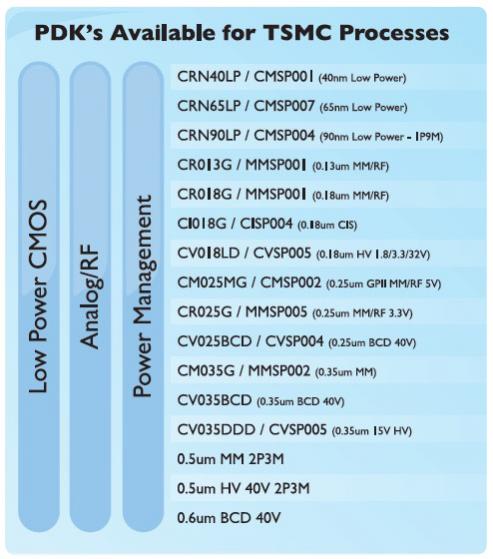

Many engineers think of Silvaco as suppling only TCAD tools, however that’s not really true because they’ve assembled a custom IC design flow of tools that support many PDKs at TSMC:

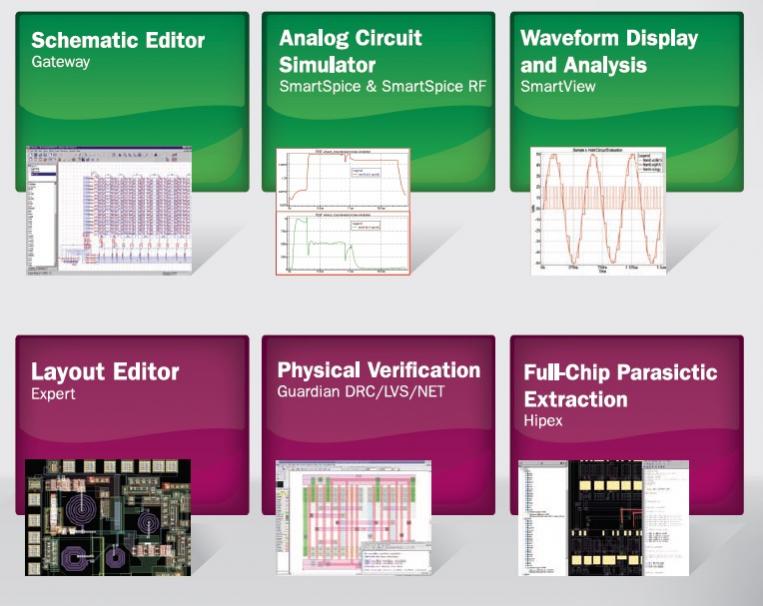

EDA Tools for Custom IC Design

AMS designers can build their next IoT products using schematic capture, SPICE circuit simulation, waveform viewing, layout editor, DRC, LVS and parasitic extraction tools. Silvaco’s SPICE circuit simulator is called SmartSpice and it has been upgraded to:

- Simulate faster by using a new parallel algorithm

- Model certified at 16 nm

- ETMI reliability supported

- Soft Error Reliability

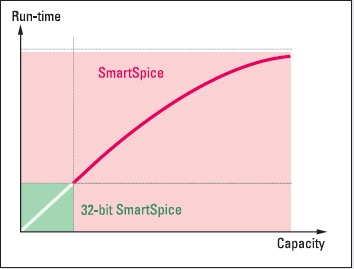

Improved capacity and performance

Related: Modeling and Analysis of Single Event Effects (SEE)

SmartSpice is used by circuit designers for library, memory and critical path characterization and it also has built-in optimizers.

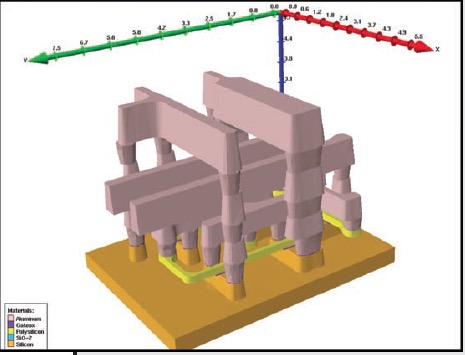

In SPICE circuit simulation you need to have netlists with extracted parasitics to get the most accurate results, and the 3D RC extractor from Silvaco is called Clever. Memory cell design require accurate parasitics in order to tune RAM performance goals and catch all of the capacitive coupling effects caused by 3D layout structures like FinFETs.

3D structure of an SRAM cell

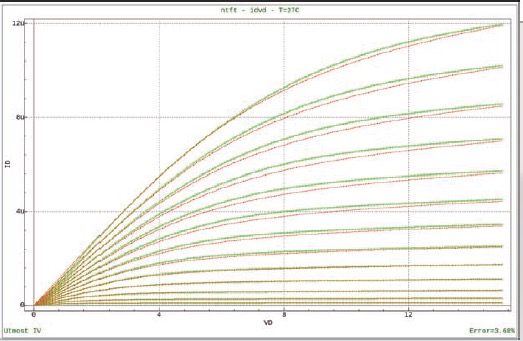

SPICE models are created by the Utmost IV tool, and many different device types are supported: TFT, UOTFT, BSIM-CMG for FinFETs, HSIM-HV2 for high voltage devices, BJT, SOI, JFET, Diode, FRAM.

TFT example fit plot using the RPI a-Si TFT model

Related: SiC and Si Power Devices

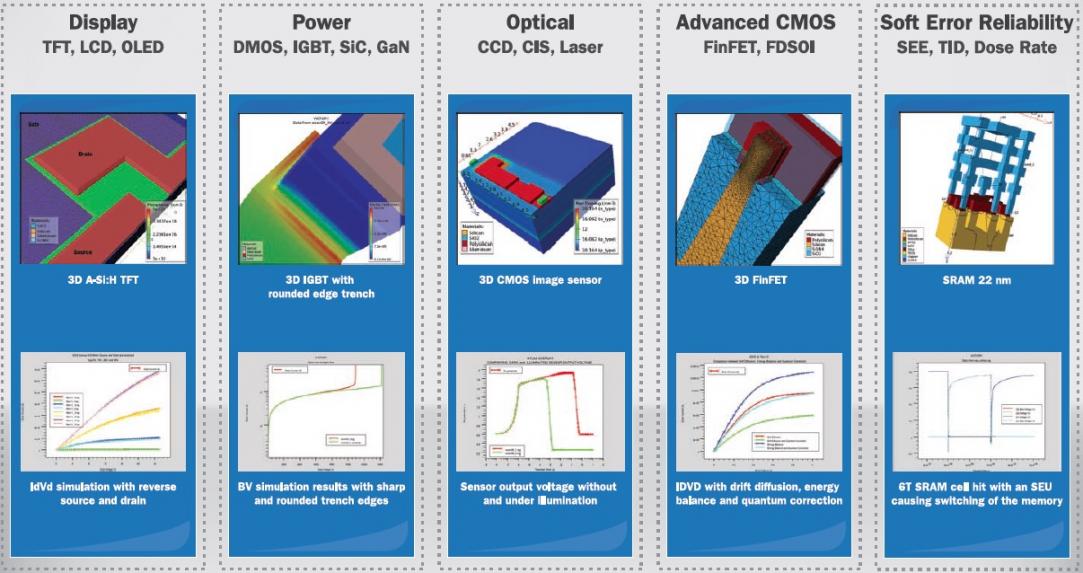

On the TCAD side engineers can virtually model diverse semiconductor technologies for: Displays, Power devices, Optical, FinFET, FD-SOI and even soft error reliability. Victory is the product name for this TCAD modeling and it supports 1D, 2D and 3D.

Related – TCAD to SPICE

I think that you’ll agree that Silvaco has a lot more than just TCAD tools to offer semiconductor engineers today, because circuit simulation and IC CAD tools are also included in their tool flow. Another factor that you need to know about Silvaco is that their tools are affordable compared to the big three in EDA. 2014 marks the 30th year in business for Silvaco, which is quite an accomplishment in this competitive industry.

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.