There’s a new blogger in town, Kelvin Low from GLOBALFOUNDRIES. Kelvin was a process engineer for Chartered Semiconductor before moving on to product marketing for GF. His latest post talks about the GF 28nm SLP which is worth a read. There was quite the controversy over this Gate-First HKMG implementation of 28nm that IBM/GF/Samsung… Read More

CEO Interview with Dave Kelf, CEO of Breker Verification SystemsIn the functional verification space, Breker Verification Systems stands…Read More

CEO Interview with Dave Kelf, CEO of Breker Verification SystemsIn the functional verification space, Breker Verification Systems stands…Read More RISC-V: From Niche Architecture to Strategic FoundationAt the recent RISC-V Now by Andes conference,…Read More

RISC-V: From Niche Architecture to Strategic FoundationAt the recent RISC-V Now by Andes conference,…Read More Bringing mathematical rigour in the world of hardware - a journey into Formal VerificationThis interview presents the first steps of Robert…Read More

Bringing mathematical rigour in the world of hardware - a journey into Formal VerificationThis interview presents the first steps of Robert…Read More The Great Divide: A Tale of Three Hardware Emulation ArchitecturesHardware emulation arose as a necessity out of…Read More

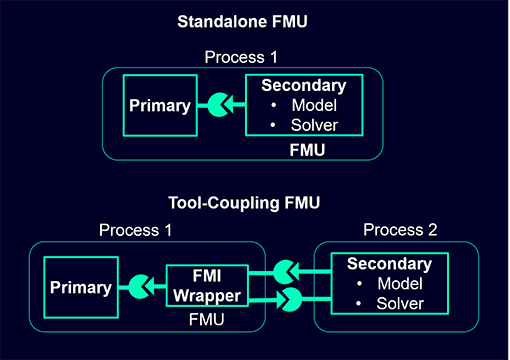

The Great Divide: A Tale of Three Hardware Emulation ArchitecturesHardware emulation arose as a necessity out of…Read More A Different Angle on Co-Simulation for SystemsCo-simulation, two or more simulations running concurrently in…Read More

A Different Angle on Co-Simulation for SystemsCo-simulation, two or more simulations running concurrently in…Read MoreWireless Application: DSP IP core is dominant

If we look back in the early 90’s, when the Global System for Mobile Communication (GSM) standard was just an emerging technology, the main innovation was the move from Analog to the Digital Processing of the Signal (DSP), allowing to make unlimited manipulation to an Analog signal, once digitized by the means of a converter (ADC).… Read More

Custom IC and AMS Tool Flow with Synopsys

The big three EDA companies all have Custom IC and AMS tool flows as shown in the following comparison table:… Read More

Hardware Intelligence for Low Power

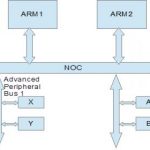

Low power is the hottest topic these days. The designers of hardware and software are trying to find instances where they can save power . This article tries to identify the role that can be played by the hardware which traditionally it is always software who drives it.… Read More

Wiring Harness Design

In 2003 Mentor acquired a company doing wiring harness design. Being a semiconductor guy this wasn’t an area I’d had much to do with. But more than most semiconductor people I expect.

But back when I was an undergraduate, I had worked as a programmer for a subsidiary of Philips called Unicam that made a huge range of spectrometers… Read More

A Brief History of Semiconductors: the Foundry Transition

A modern fab can cost as much as $10B dollars. That’s billion with a B. Since it has a lifetime of perhaps 5 years, owning a fab costs around $50 per second and that’s before you buy any silicon or chemicals or design any chips. Obviously anyone owning a fab had better be planning on making and selling a lot of chips if they are going to make… Read More

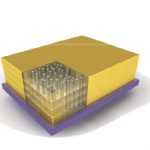

3D Memories

At DesignCon earlier this year, Tim Hollis of Micron gave an interesting presentation on 3D memories. For sure the first applications of true 3D chips are going to be stacks of memory die and memory on logic. The gains from high bandwidth access to the memory and the physically closer distance from memory to processor are huge.

Micron… Read More

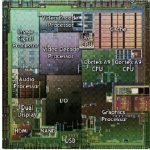

A Brief History of Cadence Design Systems

EDA software for IC and system design became a commercial business in the early 1980s. In those days, 3 companies – Daisy Systems, Mentor Graphics, and Valid Logic Systems – dominated the emerging EDA industry. However, two small startups that emerged in the early 1980s grew rapidly and merged to form Cadence Design Systems in 1988.… Read More

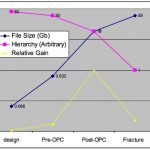

The Need for OASIS in Post-layout IC Databases

OASIS is a hierarchical IC file format used for IC designs that is gradually replacing GDS II throughout the mask data stages. The compelling reason for using OASIS has always been the reduction of file size, and speed up of processing times through the use of hierarchy and fewer translation steps.

At the 45nm node an actual M1 layer… Read More

Toshiba Corp. has cancelled plans to sell (ARM-based processor) computers …bad news for Toshiba, TI and the end user

This news announced two weeks ago is not really good news for those expecting to see this new generation of computers, running Windows RT OS and no more based on x86 processor but on ARM CPU core, coming on the market. The reason invoked by Toshiba was “delays in getting adequate supplies of components” and, even if Toshiba did not specifically… Read More

The Semiconductor Growth Numbers are Insane but the Real World Doesn’t Tally!