At DAC in June I visited and blogged about 30+ EDA and Semi IP companies, however I didn’t have time to watch the TowerJazz presentation in the Cadence Theater entitled: AMS Flow for Power Management Designs. Today I watched the 26 minute video and have summarized what I learned in this blog post.… Read More

From the Selfie to Samantha: The Next Trillion-Dollar BehaviorAt CES 2026, Samsung called it a “companion.”…Read More

From the Selfie to Samantha: The Next Trillion-Dollar BehaviorAt CES 2026, Samsung called it a “companion.”…Read More TSMC’s Record Tool Orders Hint at Another CapEx ShockwaveTSMC’s latest Board of Directors capital appropriation announcement…Read More

TSMC’s Record Tool Orders Hint at Another CapEx ShockwaveTSMC’s latest Board of Directors capital appropriation announcement…Read More CEO Interview with Nagesh Gupta of llmda.aiNagesh has built a career spanning multiple aspects…Read More

CEO Interview with Nagesh Gupta of llmda.aiNagesh has built a career spanning multiple aspects…Read More The "New Shift-Left": Why FPGA Prototyping is the Ultimate RISC-V IP SandboxIn the EDA world, "Shift-Left" has traditionally been…Read More

The "New Shift-Left": Why FPGA Prototyping is the Ultimate RISC-V IP SandboxIn the EDA world, "Shift-Left" has traditionally been…Read MoreSimulation: Expert Insights into Modeling Microcontrollers @ Renesas DevCon

“Simulation: Expert Insights into Modeling Microcontrollers” was the recent panel hot topic at Renesas DevCon2012, featuring Paolo Giustoof GM, Mark Ramseyerof Renesas, Marc Serughettiof Synopsys, Jay Yantchevof ASTC / VWorks, and Simon Davidmannof Imperas.

… Read More

SoC emulation syncs up with SuperSpeed USB

They say what adds value is to take something difficult and make it look simple. USB looks so simple when it is done right, but designers know it can be one of the more tempermental features in an SoC, especially in the latest SuperSpeed incarnation.… Read More

A Brief History of Today’s Flexible ASIC Model

There’s been an interesting trend emerging the past couple of years; a gentrification, if you will, of the ASIC business. What was thought to be a dying supply chain model has re-emerged as a health and growing segment of the semiconductor industry. Recent figures from Gartner place 2012 ASIC revenue at around $24.4 billion… Read More

Brian Bailey Interviews Kathryn Kranen

Brian Bailey at EETimes has an interesting interview with Kathryn Kranen. He says that the interview will be published in installments but the first one is up here. This first installment is mostly about how long-lived EDA companies (and others) have become since it takes a long time to build up enough revenue to be able to IPO.

She… Read More

Model Driven Development

Mentor has a webinar on Model Driven Development (MDD) for Systems Engineering, presented by Bill Chown. It is actually the first of 15 webinars. This first one is just over 30 minutes long and I assume the others will be too. The webinar focuses on embedded system development, which historically has largely been validated using… Read More

A Brief History of Semiconductors

In the last few decades, electronics has become more and more central to our lives. When I was a child the only electronics in the house was the radio and the television, both of which contained tubes. Two big things happened that upended that world: the invention of the transistor and the invention of the integrated circuit. A modern… Read More

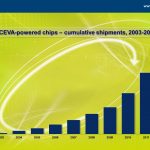

4 Billion CEVA powered Chips shipped

Why making the difference between chips and cores, when mentioning that CEVA’s customers have shipped four billion IC to date? Because that can make a big difference! Imagine for example an IP vendor selling processor IP cores to be used in massively parallel computing application, when the chip maker create a processor NxM matrix,… Read More

CDNLive Call For Papers

The Silicon Valley CDNLive, the Cadence user conference, will be on March 12-13th 2013 in Santa Clara. But the heart of CDNLive are customer presentations and the call for papers is now open. The deadline is December 4th (at 5pm PST for people who really like to come down to the wire). At this point only an abstract is required.

There… Read More

2nd International RRAM Workshop at Stanford

The 2nd International Workshop on Resistive RAM. The workshop was the second installment of an annual series organized by Stanford University and the Belgian research institute Imec. Like most RRAM workshops, this year’s event featured talks focusing on the physics of RRAM devices and their underlying switching mechanism(s).… Read More

ASML High-NA EUV is Not Ready for High-Volume Production