I will be at Semicon West from 9th to 11th July in Moscone, San Francisco. Of course there are lots of interesting sessions but here are two that I think are especially important to get a good impression of the way things are going in the future from experts. The two most interesting questions about the future are what comes after 14nm,… Read More

Captain America: Can Elon Musk Save America's Chip Manufacturing Industry?Intel has posted three consecutive years of falling…Read More

Captain America: Can Elon Musk Save America's Chip Manufacturing Industry?Intel has posted three consecutive years of falling…Read More WEBINAR: Reclaiming Clock Margin at 3nm and BelowAt 3nm and below, clock networks have quietly…Read More

WEBINAR: Reclaiming Clock Margin at 3nm and BelowAt 3nm and below, clock networks have quietly…Read More WEBINAR: HBM4E Advances Bandwidth Performance for AI TrainingThe rapid proliferation of LLMs and other AI…Read More

WEBINAR: HBM4E Advances Bandwidth Performance for AI TrainingThe rapid proliferation of LLMs and other AI…Read More Siemens Wins Best in Show Award at Chiplet Summit and Targets Broad 3D IC Design EnablementThe recent Chiplet Summit in Santa Clara was…Read More

Siemens Wins Best in Show Award at Chiplet Summit and Targets Broad 3D IC Design EnablementThe recent Chiplet Summit in Santa Clara was…Read More Siemens Fuse EDA AI Agent Releases to Orchestrate Agentic Semiconductor and PCB DesignThough terminology sometimes get fuzzy, consensus holds that…Read More

Siemens Fuse EDA AI Agent Releases to Orchestrate Agentic Semiconductor and PCB DesignThough terminology sometimes get fuzzy, consensus holds that…Read MoreWhat does 3D IC, FinFETs, and EUV have in common?

They are three of the top trending terms on SemiWiki and three of the hot topics at this year’s Semicon West:

In its 43rd year, SEMICON West is the flagship annual event for the global microelectronics industry. It is the premier event for the display of new products and technologies for microelectronics design and manufacturing,… Read More

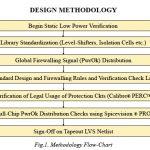

Static Low-Power Verification in Mixed-Signal SoC Designs

IC designer Shubhyant Chaturvediof AMD used EDA tools from Mentor Graphicsand Concept Engineeringto perform static, low-power verification of a mixed-signal SoC design with a combined CPU and GPU. Shubhyant presented a poster session at DAC two weeks ago in Austin, and I wanted to share it with my readers here at SemiWiki.… Read More

IC Variability Analysis at DAC

There were a handful of EDA vendors at DAC this year touting tools for IC variability analysis. On Tuesday I met with Firas Mohamed, CEO and President of Infiniscale.… Read More

A New STA Tool at DAC, No Not Cadence

The big EDA companies get big attention at DAC, however sometimes the little EDA start-ups like Arcadia Innovationhave a new product that can be overlooked. On Tuesday at DAC I met with Joey Lin, founder of Arcadia Innovation and learned about his new STA (Static Timing Analysis) tool called TimeHawk .… Read More

Physical IP Update at DAC

Last year at DAC I visited this little-known physical IP company called DXCorr, so I decided to visit them again this year and get an update.… Read More

Deploying 14nm FinFETs in your Next Mobile SoC

At DAC in Austin a design company, foundry and EDA vendor teamed up to present their experiences with 14nm FinFETs during a breakfast on Tuesday.

Panelists included:

- Ed Sperling, Semi Mfg and Design

- Anil Jain, Cavium

- Subramani Kengeri, GLOBALFOUNDRIES

- Kelvin Low, GLOBALFOUNDRIES

- Raymond Leung, Synopsys

- Bari Biswas, Synopsys

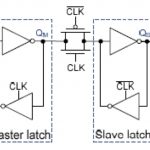

Is Your Synchronizer Doing its Job (Part 1)?

Recently, I discussed the increasing risk of metastability hazards at nanoscale geometries. These risks are significantly aggravated at low supply voltages and low temperatures and must be addressed during the design cycle of any mission critical application. This time I discuss what it takes to estimate a synchronizer’s … Read More

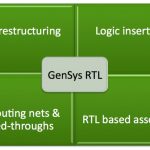

Derivative Designs Need Tools Too

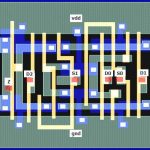

Increasingly, SoC designs consist of assembling blocks of pre-designed IP. One special case is the derivative design where not just the IP blocks get re-used but a lot of the assembly itself. For example, in the design below some blocks are added, some blocks are updated, some hierarchy is changed. But the bulk of the design remains… Read More

Increasing Automotive Semiconductor Test Quality

The growing amount of electronics within today’s automobiles is driving very high quality and reliability requirements to a widening range of semiconductor devices. At the same time, traditional fault models are becoming less effective at achieving desired silicon quality levels. Improvements in test solutions are needed… Read More

Chemical Origins of Environmental Modifications to MOR Lithographic Chemistry