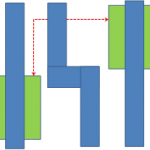

iDRM (integrated design rule manager) from Sage-DA is the world’s first and only design rule compiler. As such it is used to develop and capture design rules graphically, and can be used by non-programmers to quickly capture very complex and shape dependent design rules and immediately generate a check for them. The tool… Read More

Chemical Origins of Environmental Modifications to MOR Lithographic ChemistryIn the pursuit of advanced extreme ultraviolet (EUV)…Read More

Chemical Origins of Environmental Modifications to MOR Lithographic ChemistryIn the pursuit of advanced extreme ultraviolet (EUV)…Read More Post-Silicon Validating an MMU. Innovation in VerificationSome post-silicon bugs are unavoidable, but we’re getting…Read More

Post-Silicon Validating an MMU. Innovation in VerificationSome post-silicon bugs are unavoidable, but we’re getting…Read More Securing UALink in AI clusters with UALinkSec-compliant IPA classic networking problem is securing connections with…Read More

Securing UALink in AI clusters with UALinkSec-compliant IPA classic networking problem is securing connections with…Read MoreCMOS Biosensor Breakthrough Enables Portable Diagnostics Solution

The panel I moderated at DesignCon last week was both entertaining and enlightining. One of the panelists, Zhimin Ding, is the CEO of an emerging fabless semiconductor company and here is their story:

In the past 5 to 10 years we have seen vast advancement in medical diagnostics technology. Doctors can now use DNA or anti-body analysis… Read More

The Great Wall of TSMC

TSMC doesn’t just sell wafers, it sells trust. It’s the Colgate Ring of Confidence for fabless customers. This focus on trust started at the very beginning when Morris Chang founded TSMC over 25 years ago, and still today trust remains an essential part of their business.

When TSMC started, the big thing it brought … Read More

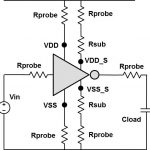

Dual Advantage of Intelligent Power Integrity Analysis

Often it is considered safer to be pessimistic in estimating IR-drop to maintain power integrity of semiconductor designs; however that leads to the use of extra buffering and routing resources which may not be necessary. In modern high speed, high density SoCs having multiple blocks, memories, analog IPs with different functionalities… Read More

Jasper Goes to DVCon

As usual, since they are firmly in the verification space, Jasper will have a number of things going on at DVCon 2014 which is March 3-6th at the Doubletree in San Jose. In the exhibition hall they are at booth #402.

Jasper will be happy to talk to you about anything, I’m sure, but the focus this year is on the JasperGold Security… Read More

Who needs DDR4 PHY running at 2667 Mbps?

As of today, DDR4 are targeting server, networking and consumer applications, and it will take another year before we use DDR4 equipped PC at home. In fact, a majority of consumers will rather buy a smartphone or tablet than a PC, most of these devices coming with PLDDR2 and only a few high-end tablets are equipped with LPDDR3 memory.… Read More

SemiWiki Job Forum

As Dan has mentioned, SemiWiki has added a Job Forum in an effort to help fit qualified people to jobs around the fabless semiconductor ecosystem. A quick survey of companies working with SemiWiki revealed over 1,000 job openings planned for 2014 and finding the right people for those positions is something we can help with.

Dan … Read More

PreEDAC Mixer

Get together with your fellow industry peers and insiders at the monthly EDAC Mixer, to the benefit of local charities. You don’t need to donate anything, you just show up and pay for your own drinks. A portion of the proceeds will go to local charities, this month to the Mountain View Educational Foundation (MVEF), a volunteer… Read More

Grid Vision 2050 – Unified & Open Across The Globe

Whenever there is good momentum in a particular technology, IEEEtakes major initiative to standardize the procedures, formats, methods, measurements etc. involved in the technology to proliferate it for the advantage of wider community. And that becomes successful by active participation and collaboration of both producers… Read More

Why Intel 14nm is NOT a Game Changer!

On one hand the Motley Fool is saying, “Intel 14nm could change the game” and on the other hand the Wall Street Cheat Sheet is saying, “Intel should shut down mobile”. SemiWiki says Intel missed mobile and should look to the future and focus on wearables and in this blog I will argue why.

Let’s look back to 2009 when Intel and TSMC signed… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era