One of the benefits of spending the last 30 years working in Silicon Valley and publishing a fabless semiconductor book is that I get invitations to speak at events I would normally be attending. Being on the other side of the podium is truly a unique experience and one worth pursuing, absolutely. This month I spoke at #51DAC about … Read More

Chemical Origins of Environmental Modifications to MOR Lithographic ChemistryIn the pursuit of advanced extreme ultraviolet (EUV)…Read More

Chemical Origins of Environmental Modifications to MOR Lithographic ChemistryIn the pursuit of advanced extreme ultraviolet (EUV)…Read More Post-Silicon Validating an MMU. Innovation in VerificationSome post-silicon bugs are unavoidable, but we’re getting…Read More

Post-Silicon Validating an MMU. Innovation in VerificationSome post-silicon bugs are unavoidable, but we’re getting…Read More Securing UALink in AI clusters with UALinkSec-compliant IPA classic networking problem is securing connections with…Read More

Securing UALink in AI clusters with UALinkSec-compliant IPA classic networking problem is securing connections with…Read MoreNoise-Coupled Analysis for Automotive ICs at DAC

My favorite method to learn about EDA tools at DAC is by listening to actual IC designers, so on June 3rd I heard Jacob Bakker from NXP talk about his experience with noise coupled analysis for advanced mixed-signal automotive ICs.… Read More

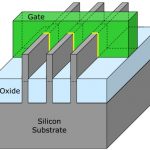

Intel & Ansys Enable 14nm Chip Production

In the semiconductor industry, it feels great to hear about the process technology shrinking to lower nodes along with innovative transistor structures that offer major gains in PPA (Power, Performance and Area). However, it requires huge investment of capital, time and effort from foundries to conceptualize, prototype and… Read More

On the Road from Makers to Consumers

It’s time to break with conventional thinking. For decades, the measure of success for semiconductors has been OEM design wins. Most consumers haven’t known, or cared, about what is inside their electronic gadgets, as long as they work. That may be about to change, because a new intermediary is finding its voice – and being… Read More

Workshop: Embedded Applications and Kernels

Design Automation Conference Workshop on Suite of Embedded Applications and Kernels

In June, the first Suite of Embedded Applications and Kernels, or SEAK, workshop at the 2014 Design Automation Conference in San Francisco introduced a new Defense Advanced Research Projects Agency program in the area of embedded system benchmarking… Read More

A Brief History of QuickLogic

Quicklogic was founded in 1988 as a fables semiconductor company supplying anti-fuse devices. In fact VLSI Technology, where I was working at the time, was their foundry.

Although today anti-fuse is often used as a generic word for one-time-programmability, the origins of the name are grounded in reality. In a fuse, like the things… Read More

SpyGlass CDC: A Comprehensive solution for addressing CDC issues

About a decade ago, semiconductor designs had just a few asynchronous clocks which were easily managed by designers through the process of manual design reviews. The situation today is completely different. An SoC can have hundreds of asynchronous clocks, driving different complex functions, spread across various IPs, supplied… Read More

Embedded Vision Summit: the How-to and the How-to

When I realized I had the opportunity to attend the Embedded Vision Summit (EVS) if I would change a return flight to a day earlier, I didn’t hesitate. Thankfully I was able to change my flight without any nuisance fee from the airline, and attended EVS.

There were two “How-to’s” at this Summit:

- The algorithmic

What is Authentication and Why Should You Care?

Authentication means making sure that something is real, just like it sounds.In the real world, authentication has many uses. One of the most recognizable is anti-counterfeiting, which means validating the authenticity of a removable, replaceable, or consumable client. Examples include system accessories, electronic … Read More

TSMC (TSM) is Having Another SoC Year!

TSMC’s stock has more than doubled in the last five years. Coincidentally that is when I started blogging about TSMC. QCOM stock has experienced a similar doubling during this time as have other TSMC customers. The question is: What is next for TSMC? As I have mentioned before, you would be better off taking stock tips from your dog… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era