Last week I was traveling in Munich attending the MunEDA User Group meetingso I missed a live webinar on the topic of optimizing for power at RTL. I finally got caught up in my email this week and had time to view this 47 minute webinar, presented by Guillaume Boilletof Atrenta. He recommended using a combination of automatic, semi-automatic… Read More

CEO Interview with Nagesh Gupta of llmda.aiNagesh has built a career spanning multiple aspects…Read More

CEO Interview with Nagesh Gupta of llmda.aiNagesh has built a career spanning multiple aspects…Read More The "New Shift-Left": Why FPGA Prototyping is the Ultimate RISC-V IP SandboxIn the EDA world, "Shift-Left" has traditionally been…Read More

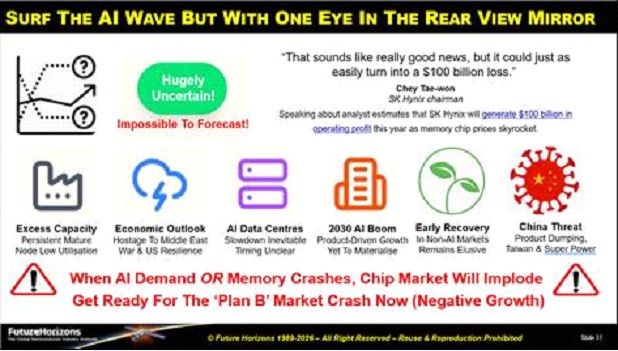

The "New Shift-Left": Why FPGA Prototyping is the Ultimate RISC-V IP SandboxIn the EDA world, "Shift-Left" has traditionally been…Read More The Semiconductor Growth Numbers are Insane but the Real World Doesn’t Tally!May’s WSTS Report saw March’s total monthly semiconductor…Read More

The Semiconductor Growth Numbers are Insane but the Real World Doesn’t Tally!May’s WSTS Report saw March’s total monthly semiconductor…Read More SiFive’s P570 Gen 3 Pushes RISC-V Further Into the AI EraWith the launch of its new P570 Gen…Read More

SiFive’s P570 Gen 3 Pushes RISC-V Further Into the AI EraWith the launch of its new P570 Gen…Read More CEO Interview with Dr. Jekaterina Viktorova of SyentaDr. Jekaterina (Jeka) Viktorova is the CEO and…Read More

CEO Interview with Dr. Jekaterina Viktorova of SyentaDr. Jekaterina (Jeka) Viktorova is the CEO and…Read MoreSolution for PI, TI & SI Issues in 3D-ICs

As we move towards packing more and more functionalities and increasing densities of SoCs, the power, thermal and signal integrity issues keep on rising. 3D-IC is a great concept to stack multiple dies on top of each other vertically. While it brings lot of avenues to package dies with multiple functions together, it has challenges… Read More

IC Place and Route for AMS Designs

High-capacity IC place and route (P&R) tools can cost $200K and more to own from the big three vendors (Cadence, Synopsys, Mentor), but what about IC designs that are primarily Big Analog and Little Digital? In the EDA world we often have multiple choices for tools, and there are affordable alternatives to place and route out… Read More

Filling the Gap between Design Planning & Implementation

As every other person is talking about IoT today, Michael Munsey of Dassault Systemes looks at this trend in the context of critical success factors and Dassault’s strategy towards providing semiconductor solution that integrates the design chain and continues to keep the semiconductor eco-system healthy and profitable. … Read More

Verification plans overcome hope-based coverage

Coverage is an important yet elusive metric for design verification. It often seems 90% of coverage comes with 10% of the effort, and getting the final 10% covered takes the remaining 90% of a project. Usually, it takes another tool or methodology to get at the 10% the first tool missed. With 100% closure difficult, most teams inspect… Read More

IC Design at ZMDI

As a blogger I have the privilege of meeting many IC designers from around the world, mostly through contact on LinkedIn or from connecting at trade shows. Through a contact at DACI met up with Achim Graupner, a manager of methodology and design automation from ZMDI, then asked him for an interview to understand how his group does … Read More

Predicting Component Temperature Early in Design

In today’s electronics with multiple functions working together, heat generation is on the rise; sometimes it becomes intolerable. In fact components running at different temperatures can cause timing issues, and very high temperatures can lead to operational issues such as latch-up. An electronic system can contain chips,… Read More

Xilinx Boards Make a Great Christmas Gift!

Ok, first thing first, Happy Thanksgiving! For the Miller’s as I get older, it is new traditions as some old ones have passed on. Memories are great and new ones to make. So you know the great debate right?

These poor people working Thanksgiving to sell some tablet or smart phone to save a few bucks. Those that must work, my condolences… Read More

Rock for CASA, December 6th

It is the holiday season so time to get together with your friends and colleagues in EDA, IP and semiconductor at the third annual event raising money for Court Appointed Special Advocates (CASA) (www.casaofsantacruz.org). This is the third event that Heart of Technology has worked with CASA. CASA has local organizations and … Read More

‘Tis the season for 4K UHD and HEVC

4K UHD TVs were all dressed up at CES 2014 with no content to show. The good news for the 2014 holiday season is the industry has converged on one set of standards for display, interfacing, and encoding, so consumers should not be left marooned in an instant replay of the 3DTV hype-crash cycle. It may be a bit longer before everyone can… Read More

From the Selfie to Samantha: The Next Trillion-Dollar Behavior