What if you and I want to exchange encrypted messages? It seems like something that will increasingly be desired given all the NSA/Snowden revelations and all the other snooping shenanigans. The joke going around is that the motto of the NSA is really “Yes We Scan,” which sort of sums it up.

Encryption is essentially scrambling a … Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data CenterAt the TERAFAB launch event in Austin on…Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data CenterAt the TERAFAB launch event in Austin on…Read More Synopsys Advances Hardware Assisted Verification for the AI EraAt the 2026 Synopsys Converge Event, Synopsys announced…Read More

Synopsys Advances Hardware Assisted Verification for the AI EraAt the 2026 Synopsys Converge Event, Synopsys announced…Read More Chemical Origins of Environmental Modifications to MOR Lithographic ChemistryIn the pursuit of advanced extreme ultraviolet (EUV)…Read More

Chemical Origins of Environmental Modifications to MOR Lithographic ChemistryIn the pursuit of advanced extreme ultraviolet (EUV)…Read More Post-Silicon Validating an MMU. Innovation in VerificationSome post-silicon bugs are unavoidable, but we’re getting…Read More

Post-Silicon Validating an MMU. Innovation in VerificationSome post-silicon bugs are unavoidable, but we’re getting…Read MoreG.fast on the copper quick road for broadband

After a four year gestation period typical of global communications standards, G.fast has reached the point where chipset makers can implement parts against stable specifications. Formal approval of the physical layer spec, G.9701, is expected by the end of 2014. G.9700, dealing with power spectral density issues, was approved… Read More

Imec and Coventor Partner Up

Today imec and Coventor announced a joint development project for 10nm and 7nm process development. Imec, which is in Leuven Belgium, is a partner with pretty much all the semiconductor companies that are planning work at these advanced nodes. It mostly does pre-competitive research and development. This type of research is … Read More

Xilinx UltraFast Design Methodology Guide will save you time and money

Well today, i’m easing my way back in from vacation. Took a camper, 6 kids, 1 wife with bun in the oven and saw the great USA. 17 States, roughly 5500 miles. It was great fun and tiring at the same time. The Grand Canyon was a blessing but I really enjoyed the ‘The Four Corners‘ where UT, CO, NM, AZ all meet. I had each kid… Read More

Designing Hardware with C++ and its Advantages

Very recently, I was seeing intense discussions on the need for agile hardware development just like agile software and ideas were being sought from experts as well as individuals. While in software world it has already evolved, in hardware world it’s yet to see the shift in paradigm. My point is that the end goal of agile hardware… Read More

The IoT and the Forbidden Fruit

A tremendous froth of press and promotion has arisen in the last year concerning the Internet of Things. Nearly every High Tech firm on the globe has begun to advertise their offerings as an integral part of it, positioning their products and services as both essential to the IoT and as a vital component of its future. As the smartphone… Read More

Cliff Hou at TSMC OIP

I attended Cliff Hou’s keynote at TSMC OIP Forum earlier this month. OIP is a huge undertaking. It currently has over 100 ecosystem partners, 10 technology generations, 7600+ IPs, 60+ EDA tools, 7000+ tech files and 150+ PDKs.

Most of Cliff’s presentation gave details on where TSMC are with the various processes. … Read More

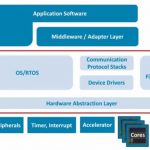

3 reasons to focus on hardware dependent software

Why is software for modern SoCs so blasted expensive to develop? One reason is more software is being developed at the kernel layer – hardware dependent software, or HdS. Application software often assumes the underlying hardware, operating system, communication stacks, and device drivers are stable. For HdS, this flawed assumption… Read More

Sensing, Processing and Connecting: IoT Fundamentals

Internet of Things, or Internet of Everything, is certainly the buzzword of the year. Does IoT describe one product family? Not really as the acronym describes a family of concepts, each of these concepts could effectively be turned into a family of products, if this concept reach the market, or fulfill a market need. Nevertheless… Read More

A Brief History of ASTC and VLAB Works

When I worked for VaST our engineering was in Sydney Australia. To my surprise there was another, entirely independent, group working on virtual platform modeling and tools in another place in Australia, in Adelaide. Is there something in the Fosters? They had originally been part of Motorola Corporate R&D and Software Group,… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center