Ever since I started talking about Virtual Fabrication I have mostly looked at it from the manufacturers’ perspective, where it has obvious benefits to develop and model new process technology. But what about the fabless design concept and indeed even the semiconductor IP world that has spawned from it as well? It seems that Virtual… Read More

Enabling RISC-V & AI Innovations with Andes AX45MPV Running Live on S2C Prodigy S8-100 Prototyping SystemQualifying an AI-class RISC-V SoC demands proving that…Read More

Enabling RISC-V & AI Innovations with Andes AX45MPV Running Live on S2C Prodigy S8-100 Prototyping SystemQualifying an AI-class RISC-V SoC demands proving that…Read More DAC News – A New Era of Electronic Design Begins with Siemens EDA AIAI is the centerpiece of DAC this year.…Read More

DAC News – A New Era of Electronic Design Begins with Siemens EDA AIAI is the centerpiece of DAC this year.…Read More Arteris at the 2025 Design Automation Conference #62DACKey Takeaways: Expanded Multi-Die Solution: Arteris showcases its…Read More

Arteris at the 2025 Design Automation Conference #62DACKey Takeaways: Expanded Multi-Die Solution: Arteris showcases its…Read MoreFull-Custom Low Power Design Methodology

Digital designers have used logic optimization and logic synthesis for decades as a means to produce more optimal designs with EDA tools. On the analog and transistor-level side of design the efforts to automatically optimize for speed or power have generally been limited to circuits with only a handful of transistors. These … Read More

Atrenta @ #51DAC Must See!

Last year at DAC, we launched the RTL Signoff platform and our customers responded enthusiastically. We even had a few other EDA companies follow our lead. So what have we been up to since then?

Visit us at DAC this June and learn how we have expanded our industry leading RTL Signoff solutions to handle the next set of challenges in SoC… Read More

Intel’s SoC Challenge!

Innovation is the cornerstone of the semiconductor industry and as history has shown, the majority of semiconductor innovation has come from fabless companies. Apple computer is my favorite example since they went from selling mother boards to computer hobbyists in the 1970’s to being one of the largest and most influential … Read More

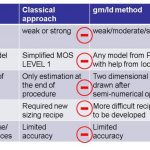

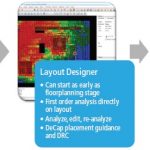

A Collaborative Approach Yields Better PI for PCBs

The power integrity (PI) of a system is an extremely important aspect to be looked at all levels – chip, package and PCB for overall reliability of the system. At the PCB level, a DC analysis, usually based on IR drop, must ensure that adequate DC voltage, satisfying all constraints of current density and temperature, is delivered… Read More

Intel’s Manufacturing Lead Explained

The calls from Wall Street keep coming with basically the same set of questions: “Does Intel really have a 2-3 year process lead? Can Intel lead the foundry segment? Can Intel Lead the Mobile SoC Segment?” The feeling amongst the buy and sell side investment people is that unless Intel can lead a market they will not stay in it… Read More

Secret to Beating Your FPGA Competitor’s Design

Can I ask you a personal question dear reader? It is only fair, you know so much about me and all, so here goes… Why are you still hand coding you’re FPGA design? Surely you are not hand coding interfaces, like PCie, SRIO, DDR, GbE, JESD204B, HMC etc… Correct? OK, why then are you still hand coding the guts of the world’s best, super-duper… Read More

Low Power Design

So you want to do a low power design. Join the club. Who doesn’t? Today all designs are low power, it is the biggest constraint on what we can do on a chip. Power down; power domains, variable clock rates, mixed Vt libraries. Every trick is needed. And that is not even enough. We get to put our phones on charge each evening and there… Read More

Calypto @ #51DAC Must See!

DAC 2014 in San Francisco promises plenty of new information on emerging low power techniques and faster ways to get to working, fully verified RTL using high level synthesis and formal verification. Get the latest from the industry leader in technologies for high level design and verification and low power RTL designby attending… Read More

A Paradigm Shift in the Foundry Supply Chain!

Samsung has plenty to talk about this year at DAC. The FD-SOI partnership with STMicroelectronics for example. Also the Samsung GLOBALFOUNDRIES 14nm partnership. Thus the “Paradigm Shift in the Foundry Supply Chain” theme. Samsung is also leading the pack with giveaways!

Flynn Was Right: How a 2003 Warning Foretold Today’s Architectural Pivot