You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

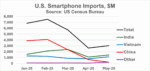

Our Semiconductor Intelligence June Newsletter showed how U.S. imports of smartphones have been on a downward trend since January 2025, led by China. Other key electronic products have also experienced sharp drops in U.S. imports from China.F

U.S. smartphone imports in May 2025 were $3.03 billion, up slightly from April but … Read More

Geoffrey Hinton, dubbed the “Godfather of AI,” joins Steven Bartlett on “The Diary of a CEO” podcast to discuss his pioneering work in neural networks and his growing concerns about AI’s dangers. Hinton, a Nobel Prize-winning computer scientist, explains how he advocated for brain-inspired… Read More

Digital audio processing is evolving into an art form, particularly in high-end applications such as automotive, cinema, and home theater. Innovation is moving beyond spatial audio technologies to concepts such as environmental correction and spatial confinement. These sophisticated soundscapes are driving a sudden increase… Read More

Agentic methods are hot right now since single LLM models seem limited to point tool applications. Each such application is impressive but still a single step in the more complex chain of reasoning tasks we want to automate, where agentic methods should shine. I have been hearing that software engineering (SWE) teams are advancing… Read More

By Mark Tawfik

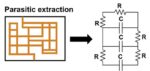

Parasitic extraction is essential in integrated circuit (IC) design, as it identifies unintended resistances, capacitances, and inductances that can impact circuit performance. These parasitic elements arise from the layout and interconnects of the circuit and can affect signal integrity, power consumption,… Read More

As the new name reflects, chip and system design were a major focus at DAC. So was the role of AI to enable those activities. But getting an AI-enabled design flow to work effectively across chip, subsystem and system-level design presents many significant challenges. One important one is effectively managing the vast amount of… Read More

As AI, HPC, and networking applications demand ever-higher compute and bandwidth, SoC complexity continues to grow. Traditional 50M ASIC equivalent gate FPGA prototyping systems have become less effective for full-chip verification at scale. Addressing this challenge, S2C introduced the Prodigy S8-100 Logic system, powered… Read More

The explosion of artificial intelligence (AI) is transforming the data center landscape, pushing the boundaries of compute, connectivity, and memory technologies. The exponential growth in AI workloads—training large language models (LLMs), deploying real-time inference, and scaling distributed applications—has … Read More

Since the fall of the Roman Empire, France has played a defining role in shaping Western civilization. In the 9th century, Charlemagne—a Frank—united much of Europe under one rule, leaving behind a legacy so profound he is still remembered as the “Father of Europe.” While Italy ignited the Renaissance, it was 16th-century France… Read More

Dr. Maksym Plakhotnyuk, is the CEO and Founder of ATLANT 3D, a pioneering deep-tech company at the forefront of innovation, developing the world’s most advanced atomic-scale manufacturing platform. Maksym is the inventor of the first-ever atomic layer advanced manufacturing technology, enabling atomic-precision development… Read More

ASML High-NA EUV is Not Ready for High-Volume Production