Agentic AI workloads are reshaping the compute requirements of modern data center infrastructure by shifting performance bottlenecks from GPU-centric inference to CPU-heavy orchestration and workflow management. Traditional AI inference pipelines relied primarily on GPUs performing a single forward pass, where input… Read More

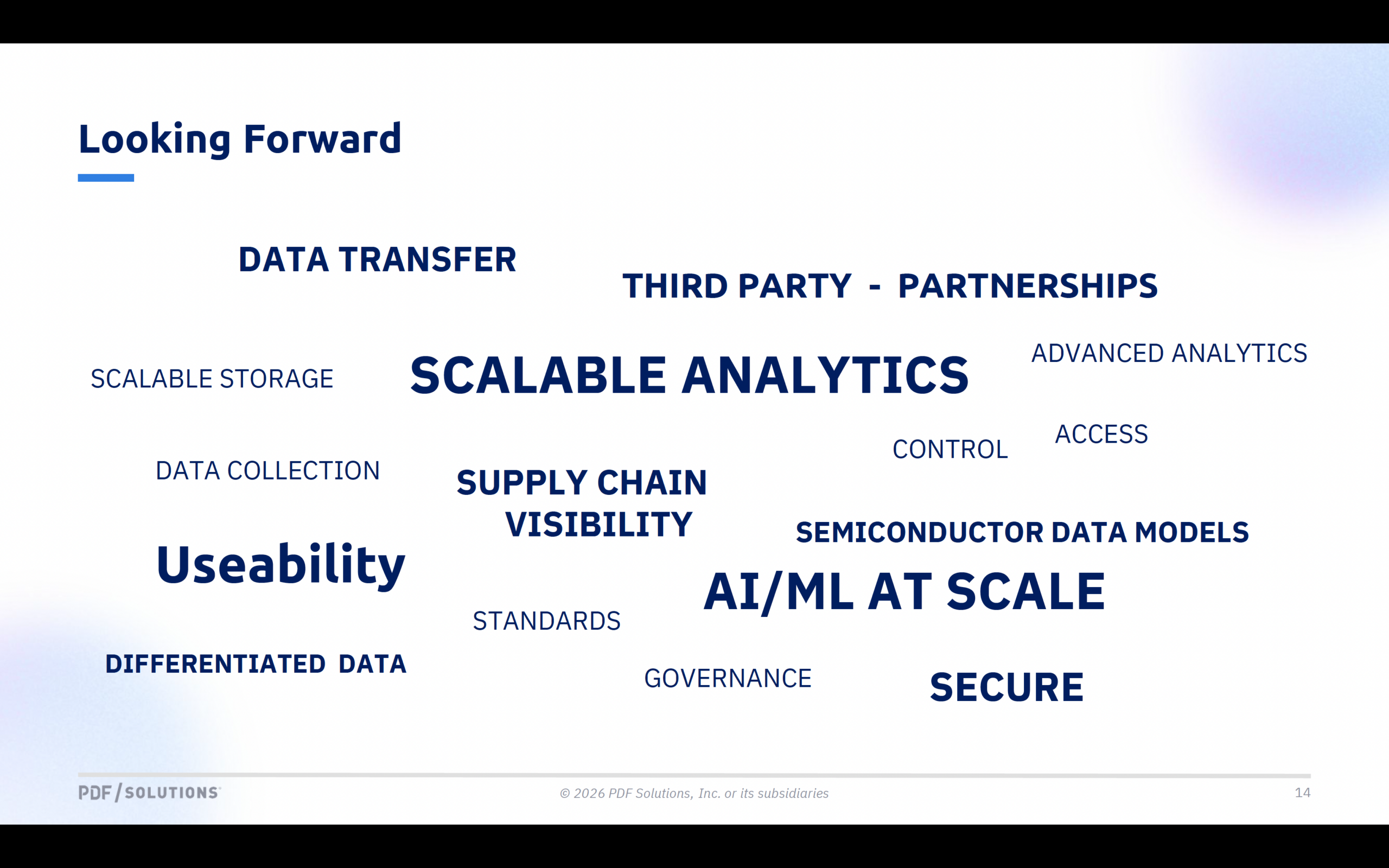

Two Paths for AI in Semiconductor Manufacturing: Platform Integration vs. Point Solutions Semiconductor manufacturing has become one of the…Read More

Two Paths for AI in Semiconductor Manufacturing: Platform Integration vs. Point Solutions Semiconductor manufacturing has become one of the…Read More Carbon in the Age of AI Chips: What the Semiconductor Industry Needs to Know This Earth DayStephen Russell: Senior Technical Fellow, TechInsights Every April,…Read More

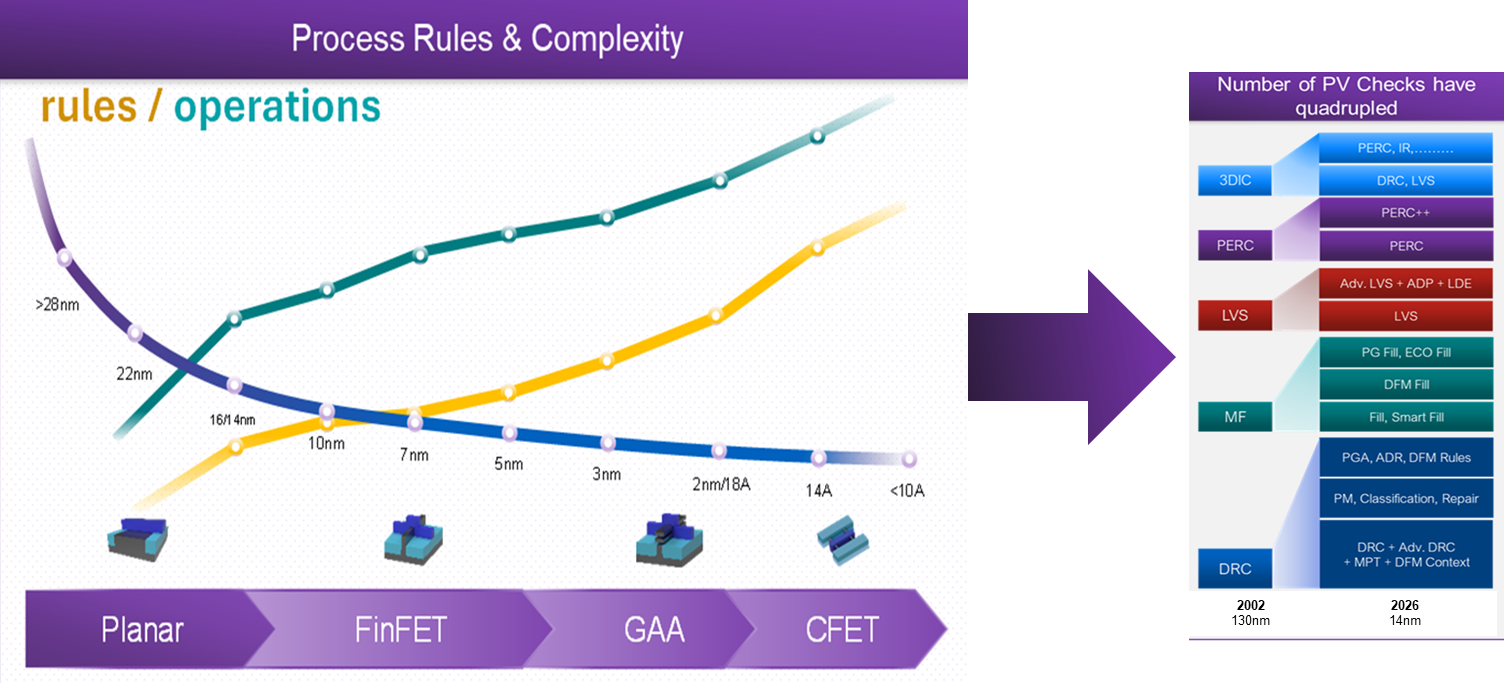

Carbon in the Age of AI Chips: What the Semiconductor Industry Needs to Know This Earth DayStephen Russell: Senior Technical Fellow, TechInsights Every April,…Read More How to Overcome the Advanced Node Physical Verification BottleneckIt is well-known that advanced semiconductor process technology…Read More

How to Overcome the Advanced Node Physical Verification BottleneckIt is well-known that advanced semiconductor process technology…Read MoreAccellera Updates at DVCon 2026

Lu Dai (chair of Accellera) and I had our regular chat at DVCon U.S. 2026. Accellera also hosted a reception in the exhibits hall, with free snacks and drinks, very well attended. We talked about what’s new in Accellera, with a particular emphasis on the recently released standard for CDC and RDC tool interoperability, also Lu’s … Read More

When a Platform Provider Becomes a Competitor: Why Arm’s Silicon Strategy Changes the Incentives

Marc Evans, Director of Business Development & Marketing, Andes Technology USA

I work at a RISC-V IP company, and I genuinely root for Arm — probably more than most people in my position would admit. Not because I’m confused about who competes with whom, but because Arm’s best move for their shareholders is also… Read More

An Upper Bound on Effective Quantum Computation?

You may think that quantum theory is fully understood but that view is not quite right. There remain open questions around the uncertainty principle, wave-particle duality, measurement collapse, and harmonizing quantum mechanics and gravitation. These concerns may seem very abstract and irrelevant to everyday applications… Read More

yieldWerx Delivers a Master Class in Co-Packaged Photonics Implementation

We all know the semiconductor industry is seeing a new era of data intensity. The industry’s response includes advanced semiconductor design strategies, the adoption of chiplets, and the integration of optical I/O and photonics to enable higher performance, faster AI computation, and increased modularity. Co-packaged photonics… Read More

RISC-V Has Momentum. The Real Question Is Who Can Deliver

RISC-V has momentum. The industry knows it. The harder question is: who can actually deliver when and where it matters?

A Shift That Changes the Stakes

On March 24, 2026, Arm made something explicit: it is now a silicon company. After decades as a neutral IP provider, Arm is moving up the stack. It’s building chips and complete solutions,… Read More

CEO Interview with Jussi-Pekka Penttinen of Vexlum

Jussi-Pekka Penttinen is the chief executive officer, chief technical officer, and cofounder of Vexlum Ltd, an advanced laser technology company. With more than 15 years of experience, he is a leading researcher in the field of Vertical External Cavity Surface Emitting Laser (VECSEL) and successfully commercialized the technology.… Read More

CEO Interview with Dr. Tony Atti of Phononic

Tony Atti, Ph.D. is Phononic’s CEO. Tony is an experienced technology entrepreneur and executive, who is passionate about disruptive technology solutions that change our lives. As CEO and Co-Founder of Phononic, Dr. Atti has led the company’s mission to sustainably transform global cooling and heating through semiconductor… Read More

Podcast EP338: How Thermo Fisher Scientific Helps Advanced Semiconductor Development with Dr. Mohan Iyer

Daniel is joined by Dr. Mohan Iyer, who serves as the vice president and general manager of the Semiconductor Business Unit at Thermo Fisher Scientific, a global leader in providing reference metrology, defect characterization, and localization equipment. These advanced systems are essential for driving innovation, accelerating… Read More

Samtec’s Strong Presence at embedded world 2026

The embedded world Exhibition & Conference recently concluded. The event is held annually in Nuremberg, Germany and has become one of the most influential gatherings for the global embedded systems community. Since its inception in 2003, the event has grown from a modest technical meeting into a large-scale international… Read More

Is Intel About to Take Flight?