This is a clear reminder of how important the semiconductor ecosystem is and how closely TSMC works with customers. The TSMC Symposium started 30 years ago and I have been a part of it ever since. This event is attended by TSMC’s top customers and partners and is the #1 semiconductor networking event of the year, absolutely.… Read More

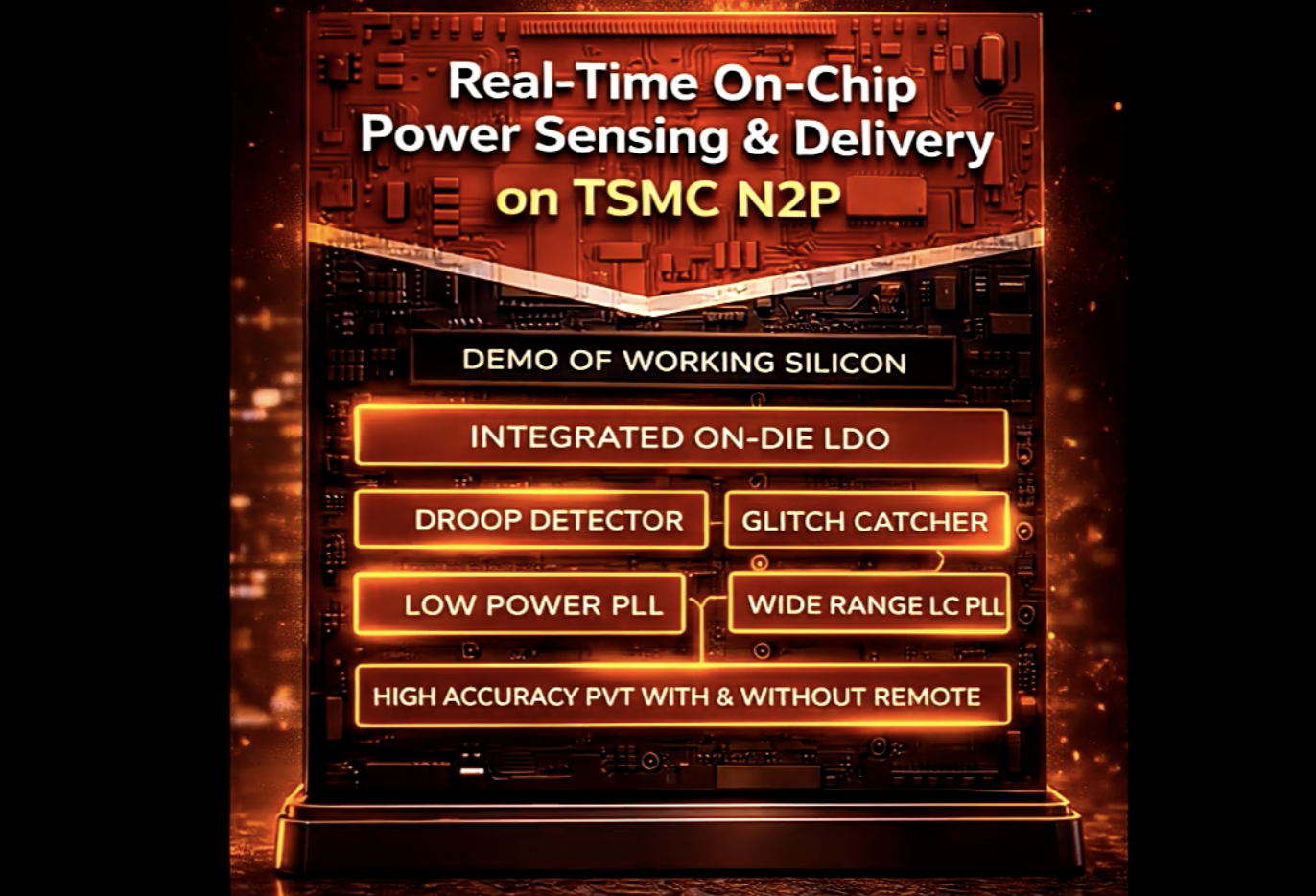

Analog Bits Demos Real-Time On-Chip Power Sensing and Delivery on N2P at the TSMC 2026 Technology SymposiumAnalog Bits has a way of stealing the…Read More

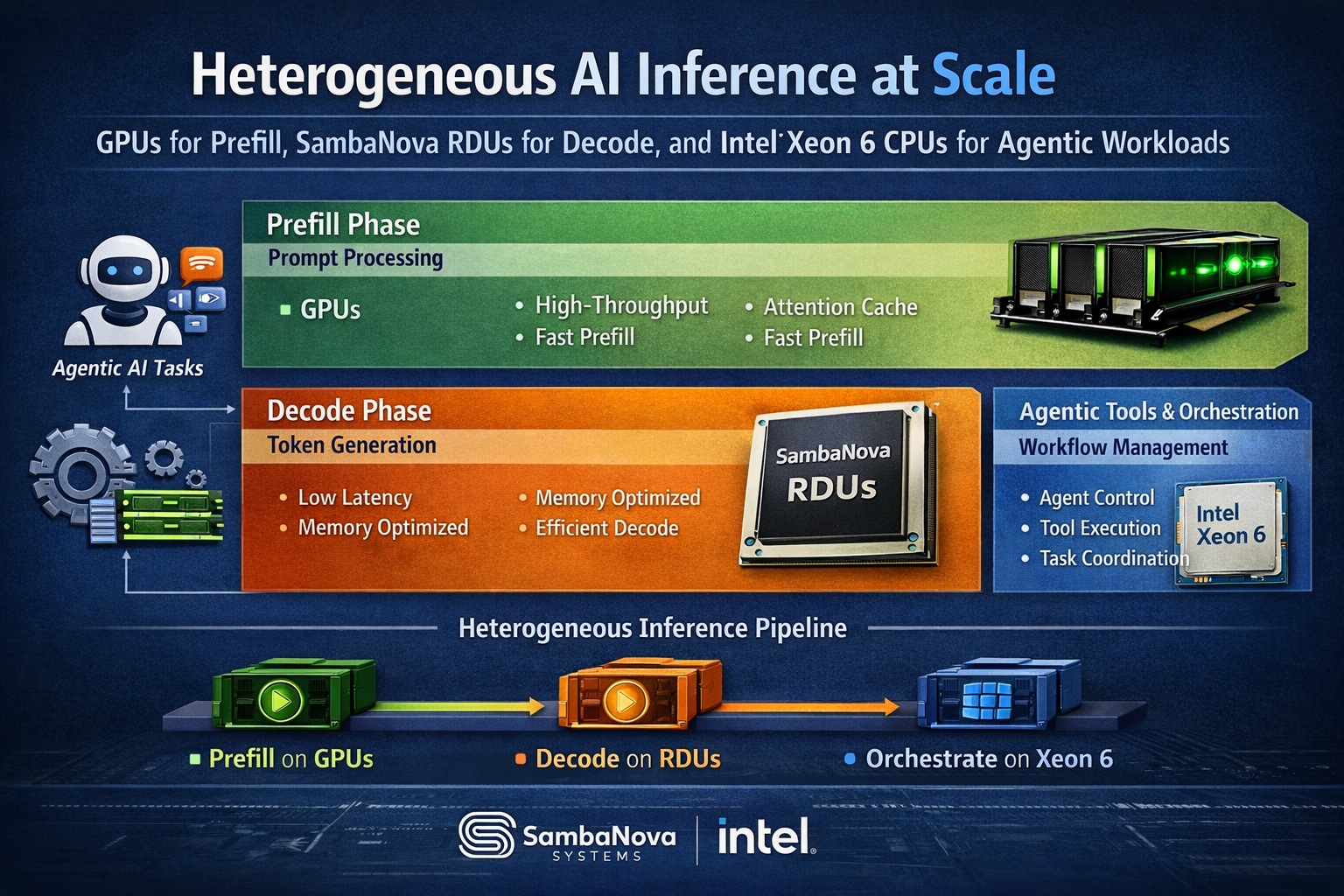

Analog Bits Demos Real-Time On-Chip Power Sensing and Delivery on N2P at the TSMC 2026 Technology SymposiumAnalog Bits has a way of stealing the…Read More Disaggregating LLM Inference: Inside the SambaNova Intel Heterogeneous Compute BlueprintSambaNova Systems and Intel have introduced a blueprint…Read More

Disaggregating LLM Inference: Inside the SambaNova Intel Heterogeneous Compute BlueprintSambaNova Systems and Intel have introduced a blueprint…Read More CEO Interview with Johan Wadenholt Vrethem of VoxoWith over two decades of experience bridging technology…Read More

CEO Interview with Johan Wadenholt Vrethem of VoxoWith over two decades of experience bridging technology…Read More TSMC to Elon Musk: There are no Shortcuts in Building Fabs!The opening of the TSMC 2026 earning call…Read More

TSMC to Elon Musk: There are no Shortcuts in Building Fabs!The opening of the TSMC 2026 earning call…Read More Speculation: Silicon’s Most Expensive CompulsionHow Time-Based Scheduling Reclaims Silicon Wasted by Speculative…Read More

Speculation: Silicon’s Most Expensive CompulsionHow Time-Based Scheduling Reclaims Silicon Wasted by Speculative…Read MoreCEO Interview with Pere Llimós Muntal of Skycore Semiconductors

Pere Llimós Muntal is the CEO and co-founder of Skycore Semiconductors, driving the strategy, business development, and growth of the company as it delivers next-generation power integrated circuit (IC) solutions for applications with extreme power density, efficiency, and form factor demands, such as data center power… Read More

Podcast EP321: An Overview of Soitec’s Worldwide Leadership in Engineered Substrates with Steve Babureck

Daniel is joined by Steve Babureck, executive vice president of strategy and president of Soitec USA. He joined the company in 2011 and held various positions including head of the finance department of the solar business in the United States, head of strategic marketing, and head of Group investor Relations in San Diego and Singapore.… Read More

ClockEdge Delivers Precision, Visibility and Control for Advanced Node Clock Networks

At advanced nodes, the clock is no longer just another signal. It is the most critical and sensitive electrical network on the chip, and the difference between meeting performance targets and missing the tape-out often comes down to a few picoseconds, buried deep inside the clock distribution network. Yet many design teams still… Read More

CEO Interview with Haber Ma of ADCERAX

Haber Ma is the CEO of ADCERAX and leads the company’s global strategy in advanced ceramic materials for semiconductor and high-performance industrial applications. With a background in engineering, precision manufacturing, and international supply chain development, he has overseen ADCERAX’s transition from a traditional… Read More

WEBINAR: Defacto’s SoC Compiler AI: Democratizing SoC Design with Human Language

Modern chip design has reached unprecedented levels of complexity. Today’s System-on-Chip (SoC) designs integrate multiple processors, complex memory hierarchies, sophisticated interconnects, and much more. All requiring orchestration using complex EDA tool flows. Months are routinely lost to configuration… Read More

An Assistant to Ease Your Transition to PSS

At times it has seemed like any development in EDA had to build a GenAI app that would catch the attention of Wall Street. Now I see more attention to GenAI being used for less glamorous but eminently more practical advances. This recent white paper from Siemens on how to help verification engineers get up to speed faster with PSS is … Read More

Accelerating NPI with Deep Data: From First Silicon to Volume

For decades, semiconductor teams have relied on traditional methods such as corner-based analysis, surrogate monitors, and population-level statistical screening for post-silicon validation. These methods served well when variability was modest, and timing paths behaved predictably. However, today’s advanced nodes… Read More

We Need to Turn Specs into Oracles for Agentic Verification

The natural language understanding now possible in LLMs has raised interest in using specs as a direct reference for test generation, to eliminate need for intermediate and fallible human translation. Sadly, specs today are not an infallible source of truth for multiple reasons. I am grateful to Shelly Henry (CEO of MooresLab)… Read More

Accelerating SRAM Design Cycles: MediaTek’s Adoption of Siemens EDA’s Additive AI Technology at TSMC OIP 2025

In the competitive vertical of mobile System-on-Chip development, SRAM plays a pivotal role, occupying nearly 40% of chip area and directly impacting yield and performance. The presentation “Accelerating SRAM Design Cycles With Additive AI Technology,” co-delivered by Mohamed Atoua of Siemens EDA and Deepesh… Read More

Is Intel About to Take Flight?