SPI, invented some four decades ago, is so successful as a low-pin-count interface for microcontrollers and processor cores that it spurred memory makers to incorporate both the physical signaling interface and advanced memory command protocols into serial flash and serial pseudo-SRAM (PSRAM) devices. Those protocols, … Read More

CEO Interview with Nagesh Gupta of llmda.aiNagesh has built a career spanning multiple aspects…Read More

CEO Interview with Nagesh Gupta of llmda.aiNagesh has built a career spanning multiple aspects…Read More The "New Shift-Left": Why FPGA Prototyping is the Ultimate RISC-V IP SandboxIn the EDA world, "Shift-Left" has traditionally been…Read More

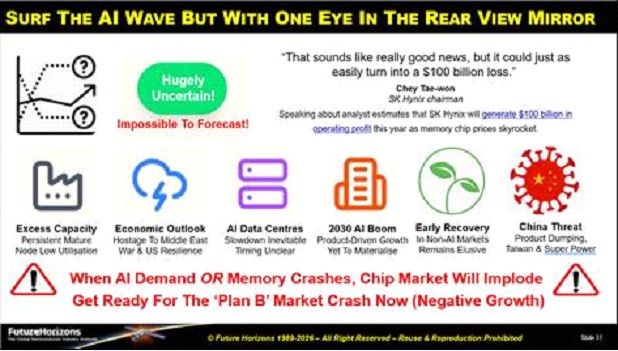

The "New Shift-Left": Why FPGA Prototyping is the Ultimate RISC-V IP SandboxIn the EDA world, "Shift-Left" has traditionally been…Read More The Semiconductor Growth Numbers are Insane but the Real World Doesn’t Tally!May’s WSTS Report saw March’s total monthly semiconductor…Read More

The Semiconductor Growth Numbers are Insane but the Real World Doesn’t Tally!May’s WSTS Report saw March’s total monthly semiconductor…Read More SiFive’s P570 Gen 3 Pushes RISC-V Further Into the AI EraWith the launch of its new P570 Gen…Read More

SiFive’s P570 Gen 3 Pushes RISC-V Further Into the AI EraWith the launch of its new P570 Gen…Read More CEO Interview with Dr. Jekaterina Viktorova of SyentaDr. Jekaterina (Jeka) Viktorova is the CEO and…Read More

CEO Interview with Dr. Jekaterina Viktorova of SyentaDr. Jekaterina (Jeka) Viktorova is the CEO and…Read MoreCEO Interview with Dr. Jekaterina Viktorova of Syenta

Dr. Jekaterina (Jeka) Viktorova is the CEO and Co-Founder of Syenta, an Australian deep-tech company developing breakthrough additive manufacturing technology for the semiconductor industry. With a background in chemistry, electrochemistry, and advanced manufacturing, she is the inventor of the core Syenta technology… Read More

Sensing. A Quantum Tech Ready for Market?

While the quantum world revolves around quantum computing, (QC) there are a couple of other quantum technologies of note. I covered one of these, quantum communication, in a recent blog. Here I’ll introduce the other, quantum sensing. The goal is to use the high sensitivity of an individual quantum state to external factors such… Read More

Beyond Tool Interoperability: The Emerging Governed Convergence Problem in Semiconductor Design

The semiconductor industry has spent decades optimizing tools. Today, however, the central challenge is no longer whether individual tools are powerful enough. The real question is whether increasingly specialized tools, domains, models, and organizations can still converge coherently into a manufacturable, reliable,… Read More

#DAC2026 Marks Another Pivotal Moment for the Semiconductor Industry

The 2026 Design Automation Conference (DAC 2026) marks another pivotal moment for the semiconductor and electronic systems industry as artificial intelligence, chiplets, heterogeneous integration, and system-level optimization redefine the future of design automation. Held July 26–29, 2026, at the Long Beach Convention… Read More

IPLM: Future Forward Webinar May 19th

Step into the future of semiconductor design management with IPLM: Future Forward, a product-led webinar showcasing the latest developments in Perforce IPLM. This focused session is designed to show how modern teams can tackle growing design complexity while still accelerating innovation.

Hosted by IPLM… Read More

From Point Solutions to Agentic AI Ecosystems: Semiconductor Process Control Depends on Its Past

Agentic AI is often presented as a revolutionary shift in semiconductor manufacturing, driven by large language models and generative AI. However, this framing overlooks an important reality: today’s advances are built on decades of prior work. As Jonathan Holt of PDF Solutions emphasizes in his recent keynote at the APCM 2026… Read More

Panel Discission: Beyond Moore’s Law and the Future of Semiconductor Manufacturing

The semiconductor industry is entering a post-Moore’s Law era in which scaling transistor density alone is no longer sufficient to sustain historical performance growth. As discussed in the panel Beyond Moore’s Law: The Future of Semiconductor Manufacturing, the industry is increasingly dependent on advanced manufacturing… Read More

CEO Interview with Matt Crowley of Scintil Photonics

Matt Crowley is Chief Executive Officer of Scintil Photonics. A physicist by training, Matt built his career transitioning advanced semiconductor technologies from development to volume manufacturing. Before Scintil, he led MEMS technology company Vesper Technologies to high-volume production and through its acquisition… Read More

Podcast EP345: The Impact of the New proteanTecs PVT Plus Sensors with Nir Sever

Daniel is joined by Nir Sever, Senior Director of Business Development at proteanTecs. Nir has over 30 years of experience in advanced VLSI engineering. Before joining proteanTecs, he served for 10 years as the COO of Tehuti Networks, a pioneer in high-speed networking semiconductors. Prior to that, he served for 9 years as Senior… Read More

From the Selfie to Samantha: The Next Trillion-Dollar Behavior