You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

I consider Dr. Aart de Geus one of the founding fathers of EDA and one of the most interesting people in the semiconductor industry. So it is not a surprise that Aart was chosen to attend the CHIPs Act signing at the White House.

Here is his current corporate bio:

Since co-founding Synopsys in 1986, Dr. Aart de Geus has expanded Synopsys… Read More

Jay Dawani is the co-founder & CEO at Lemurian Labs, a startup developing a novel processor to enable autonomous robots to fully leverage the capabilities of modern day AI within their current energy, space, and latency constraints.

Prior to founding Lemurian, Jay had founded two other companies in the AI space. He is also … Read More

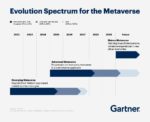

Any new technology involves a certain amount of ambiguity and myths. In the case of the Metaverse, however, many of the myths have been exaggerated and facts were misrepresented, while the Metaverse vision will take years to mature fully, the building blocks to begin this process are already in place. Key hardware and software … Read More

We need more and more complex chips and SoCs for all new applications that use the latest technologies like AI. For example, Apple’s 5nm SoC A14 features 6-core CPU, 4 core-GPU and 16-core neural engine capable of 11 trillion operations per second, which incorporates 11.8 billion transistors, and AWS 7nm 64-bit Graviton2 custom… Read More

Dan is joined by Ron Glibbery, who co-founded Peraso Technologies in 2009 and serves as its chief executive officer. Prior to co-founding Peraso Technologies, Ron held executive positions at Kleer Semiconductor Intellon, Cogency Semiconductor, and LSI Logic.

Dan and Ron explore the impact of Pareso’s unique mmWave … Read More

Rich Edelman of Siemens EDA recently released a paper on this topic. I’ve known Rich since our days together back in National Semi. And I’ve always been impressed by his ability to make a complex topic more understandable to us lesser mortals. He tackles a tough one in this paper – a complex concept (polymorphism) in a complex domain… Read More

3D IC technology development started many years ago well before the slowing down of Moore’s law benefits became a topic of discussion. The technology was originally leveraged for stacking functional blocks with high-bandwidth buses between them. Memory manufacturers and other IDMs were the ones to typically leverage this … Read More

As embedded systems continue to become more complex and integrate greater functionality, SoC developers are faced with the challenge of developing more powerful, yet more energy-efficient devices. The processors used in these embedded applications must be efficient to deliver high levels of performance within limited power… Read More

Digital Twins Simplify System Analysisby Dave Bursky on 08-15-2022 at 6:00 amCategories: EDA, Siemens EDA

The ability to digitally replicate physical systems has been used to model hardware operations for many years, and more recently, digital twining technology has been applied to electronic systems to better simulate and troubleshoot the systems. As explained by Bryan Ramirez, Director of Industries, Solutions & Ecosystems,… Read More

In the final season of “The Sopranos,” Christopher Multisanti (played by Michael Imperioli) and Anthony Soprano (James Gandolfini) lose control of their black Cadillac Escalade and go tumbling off a two-lane rural highway and down a hill. Christopher dies (spoiler alert) with an assist from Tony, before Tony calls “911” for… Read More

Captain America: Can Elon Musk Save America’s Chip Manufacturing Industry?