I have a new-found respect for Lu Dai. He is a senior director of engineering at Qualcomm, with valuable insight into the ground realities of verification in a big semiconductor company. He is on the board of directors at RISC-V International and is chairman of the board of directors at Accellera, both giving him a top-down view of… Read More

AI-Driven Automation in Semiconductor Design: The Fuse EDA AI AgentThe semiconductor industry is experiencing unprecedented growth in…Read More

AI-Driven Automation in Semiconductor Design: The Fuse EDA AI AgentThe semiconductor industry is experiencing unprecedented growth in…Read More TSMC Technology Symposium 2026: Advancing the Future of Semiconductor InnovationOne of my favorite times of the year…Read More

TSMC Technology Symposium 2026: Advancing the Future of Semiconductor InnovationOne of my favorite times of the year…Read More Synopsys Explores AI/ML Impact on Mask Synthesis at SPIE 2026The SPIE Advanced Lithography + Patterning Symposium recently…Read More

Synopsys Explores AI/ML Impact on Mask Synthesis at SPIE 2026The SPIE Advanced Lithography + Patterning Symposium recently…Read MoreSino Semicap Sanction Screws Snugged- SVB- Aftermath more important than event

-Reports of further tightening of China SemiCap Restrictions

-Likely closing loopholes & pushing back technology line

-Dutch have joined, Japan will too- So far no Chinese reaction

-SVB is toast but repercussions may be far worse

Reports of tightening semiconductor sanctions on Friday

It was reported byBloomberg of Friday… Read More

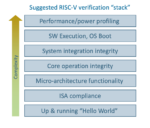

Scaling the RISC-V Verification Stack

The RISC-V open ISA premise was clearly a good bet. It’s taking off everywhere, however verification is still a challenge. As an alternative to Arm, the architecture and functionality from multiple IP providers looks very competitive, but how do RISC-V providers and users ensure the same level of confidence we have in Arm? Arm … Read More

JESD204D: Expert insights into what we Expect and how to Prepare for the upcoming Standard

Join our upcoming webinar on JESD204 and get insights into what we predict the upcoming JESD204D standard will contain, based on many years of experience working with JESD204.

Our expert speaker, Piotr Koziuk, has over a decade of experience with JESD204 standards and is a member of the JEDEC Standardization Committee. He will… Read More

Scaling AI as a Service Demands New Server Hardware

While I usually talk about AI inference on edge devices, for ADAS or the IoT, in this blog I want to talk about inference in the cloud or an on-premises datacenter (I’ll use “cloud” below as a shorthand to cover both possibilities). Inference throughput in the cloud is much higher today than at the edge. Think about support in financial… Read More

MIPI D-PHY IP brings images on-chip for AI inference

Edge AI inference is getting more and more attention as demand grows for AI processing across an increasing number of diverse applications, including those requiring low-power chips in a wide range of consumer and enterprise-class devices. Much of the focus has been on optimizing the neural network processing engine for these… Read More

SPIE Advanced Lithography Conference 2023 – AMAT Sculpta® Announcement

The SPIE Advanced Lithography Conference is the semiconductor industries premier conference on lithography. The 2023 conference was held the week of February 27th and at the conference Applied Materials announced their Sculpta® pattern shaping tool. Last week I had an opportunity to interview Steven Sherman the Managing … Read More

Podcast EP147: CachQ’s Harnessing of Heterogeneous Compute with Clay Johnson

Dan is joined by Clay Johnson, CEO and co-founder of CacheQ Systems. Clay has more than 25 years of executive management experience across a broad spectrum of technologies including computing, security, semiconductors and EDA tools.

Dan discusses the CacheQ QCC development platform with Clay. This platform enables software… Read More

Cadence Hosts ESD Alliance Seminar on New Export Regulations Affecting EDA and SIP March 28

Anyone interested in learning about general trade compliance concepts or how export control and sanction regulations affect the electronic systems design ecosystem will want to attend the upcoming ESD Alliance export seminar. It will be hosted by Ada Loo, chair of the ESD Alliance Export Committee and Cadence’s Group Director… Read More

AAA Hypes Self-Driving Car Fears

The AAA (U.S. auto club) must have AGHD (attention-getting deficit disorder). The headline from the organization’s latest research is: “Fear of Self-Driving Cars is on the Rise.” That should straighten things out, right?

The survey was conducted across a representative sample of U.S. households, according to the reported… Read More

Beyond Moore’s Law: High NA EUV Lithography Redefines Advanced Chip Manufacturing